- 您现在的位置:买卖IC网 > PDF目录377557 > IS61DDB21M36-250M3 (INTEGRATED SILICON SOLUTION INC) 36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 2) CIO Synchronous SRAMs PDF资料下载

参数资料

| 型号: | IS61DDB21M36-250M3 |

| 厂商: | INTEGRATED SILICON SOLUTION INC |

| 元件分类: | DRAM |

| 英文描述: | 36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 2) CIO Synchronous SRAMs |

| 中文描述: | 1M X 36 DDR SRAM, 0.35 ns, PBGA165 |

| 封装: | 15 X 17 MM, 1 MM PITCH, FBGA-165 |

| 文件页数: | 18/25页 |

| 文件大小: | 421K |

| 代理商: | IS61DDB21M36-250M3 |

18

Integrated Silicon Solution, Inc. — 1-800-379-4774

Rev. B

2/22/05

ISSI

36 Mb (1M x 36 & 2M x 18)

DDR-II (Burst of 2) CIO Synchronous SRAMs

IEEE 1149.1 TAP and Boundary Scan

The SRAM provides a limited set of JTAG functions to test the interconnection between SRAM I/Os and

printed circuit board traces or other components. There is no multiplexer in the path from I/O pins to the RAM

core.

In conformance with IEEE Standard 1149.1, the SRAM contains a TAP controller, instruction register,

boundary scan register, bypass register, and ID register.

The TAP controller has a standard 16-state machine that resets internally on power-up. Therefore, a TRST

signal is not required.

Signal List

TCK: test clock

TMS: test mode select

TDI: test data-in

TDO: test data-out

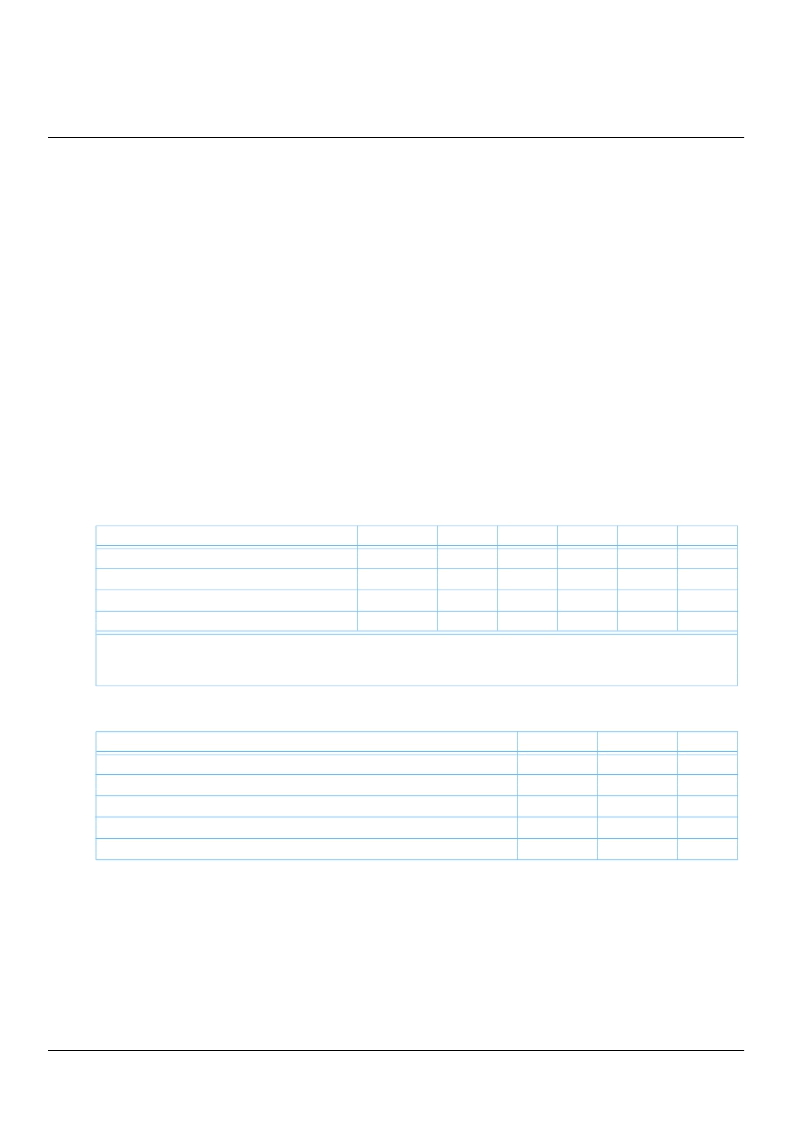

JTAG DC Operating Characteristics

(T

A

= 0 to +

70°

C)

Operates with JEDEC Standard 8-5 (1.8V) logic signal levels

Parameter

Symbol

Minimum

Typical

Maximum

Units

Notes

JTAG input high voltage

V

IH1

1.3

—

V

DD

+0.3

V

1

JTAG input low voltage

V

IL1

-0.3

—

0.5

V

1

JTAG output high level

V

OH1

V

DD

-0.4

—

V

DD

V

1, 2

JTAG output low level

V

OL1

V

SS

—

0.4

V

1, 3

1. All JTAG inputs and outputs are LVTTL-compatible.

2. I

OH1

≥

-|2mA|

3. I

OL1

≥

+|2mA|.

JTAG AC Test Conditions

(T

A

= 0 to +

70°

C, V

DD

= 1.8V -5%, +5%)

Parameter

Symbol

Conditions

Units

Input pulse high level

V

IH1

1.3

V

Input pulse low level

V

IL1

0.5

V

Input rise time

T

R1

1.0

ns

Input fall time

T

F1

1.0

ns

Input and output timing reference level

0.9

V

相关PDF资料 |

PDF描述 |

|---|---|

| IS61DDB22M18 | 36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 2) CIO Synchronous SRAMs |

| IS61DDB22M18-250M3 | 36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 2) CIO Synchronous SRAMs |

| IS61DDB41M36-250M3 | 36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 4) CIO Synchronous SRAMs |

| IS61DDB42M18 | 36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 4) CIO Synchronous SRAMs |

| IS61DDB42M18-250M3 | 36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 4) CIO Synchronous SRAMs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IS61DDB21M36-250M3L | 功能描述:静态随机存取存储器 36M (1Mx36) 250MHz DDR II Sync 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| IS61DDB21M36-275M3 | 功能描述:静态随机存取存储器 36M (1Mx36) 275MHz DDR II Sync 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| IS61DDB21M36A-250M3L | 功能描述:静态随机存取存储器 36Mb 1Mx36 165ball DDR II Sync 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

| IS61DDB22M18 | 制造商:ISSI 制造商全称:Integrated Silicon Solution, Inc 功能描述:36 Mb (1M x 36 & 2M x 18) DDR-II (Burst of 2) CIO Synchronous SRAMs |

| IS61DDB22M18-250M3 | 功能描述:静态随机存取存储器 36Mb 2Mbx18 DDR II Sync 静态随机存取存储器 RoHS:否 制造商:Cypress Semiconductor 存储容量:16 Mbit 组织:1 M x 16 访问时间:55 ns 电源电压-最大:3.6 V 电源电压-最小:2.2 V 最大工作电流:22 uA 最大工作温度:+ 85 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:TSOP-48 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。