- 您现在的位置:买卖IC网 > PDF目录14798 > LTC3615EUF#PBF (Linear Technology)IC REG BUCK SYNC ADJ 3A DL 24QFN PDF资料下载

参数资料

| 型号: | LTC3615EUF#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 15/32页 |

| 文件大小: | 0K |

| 描述: | IC REG BUCK SYNC ADJ 3A DL 24QFN |

| 标准包装: | 91 |

| 类型: | 降压(降压) |

| 输出类型: | 可调式 |

| 输出数: | 2 |

| 输出电压: | 0.6 V ~ 5.5 V |

| 输入电压: | 2.25 V ~ 5.5 V |

| PWM 型: | 电流模式,混合 |

| 频率 - 开关: | 400kHz ~ 4MHz |

| 电流 - 输出: | 3A |

| 同步整流器: | 是 |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-WFQFN 裸露焊盘 |

| 包装: | 管件 |

| 供应商设备封装: | 24-QFN 裸露焊盘(4x4) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

�� �

�

�

�LTC3615/LTC3615-1�

�APPLICATIONS� INFORMATION�

�4� ?� 10� 11� Ω� Hz�

�f� OSC�

�OperatingFrequency�

�Selection� of� the� operating� frequency� is� a� trade-off� between�

�efficiency� and� component� size.� High� frequency� operation�

�allows� the� use� of� smaller� inductor� and� capacitor� values.�

�Operation� at� lower� frequencies� improves� efficiency� by�

�reducing� internal� gate� charge� losses� but� requires� larger�

�inductance� values� and/or� capacitance� to� maintain� low�

�output� ripple� voltage.�

�The� operating� frequency� of� the� LTC3615� is� determined�

�by� an� external� resistor� that� is� connected� between� pin� R� T� /�

�SYNC� and� ground.� The� value� of� the� resistor� sets� the� ramp�

�current� that� is� used� to� charge� and� discharge� an� internal�

�timing� capacitor� within� the� oscillator� and� can� be� calculated�

�by� using� the� following� equation:�

�R� T� =�

�Although� frequencies� as� high� as� 4MHz� are� possible,� the�

�minimum� on-time� of� the� LTC3615� imposes� a� minimum�

�limit� on� the� operating� duty� cycle.� The� minimum� on-time�

�is� typically� 60ns,� therefore,� the� minimum� duty� cycle� is�

�equal� to� 60ns� ?� 100%� ?� f� OSC� (Hz)�

�Tying� the� R� T� /SYNC� pin� to� SV� IN� sets� the� default� internal�

�operating� frequency� to� 2.25MHz� ±20%.�

�Frequency� Synchronization�

�The� LTC3615’s� internal� oscillator� can� be� synchronized� to�

�an� external� frequency� by� applying� a� square� wave� clock�

�signal� to� the� R� T� /SYNC� pin.� During� synchronization,� the�

�top� MOSFET� turn-on� of� channel� 1� is� locked� to� the� rising�

�edge� of� the� external� frequency� source.� The� synchronization�

�frequency� range� is� 400kHz� to� 4MHz.� The� internal� slope�

�compensation� is� automatically� adapted� to� the� external�

�clock� frequency.�

�In� the� signal� path� from� the� R� T� /SYNC� clock� input� to� the�

�SW� output,� the� LTC3615� is� processing� the� external� clock�

�frequency� through� an� internal� PLL.�

�After� detecting� an� external� clock� on� the� first� rising� edge�

�of� R� T� /SYNC� the� PLL� starts� up� with� the� internal� default� of�

�2.25MHz.� The� internal� PLL� then� requires� a� certain� number�

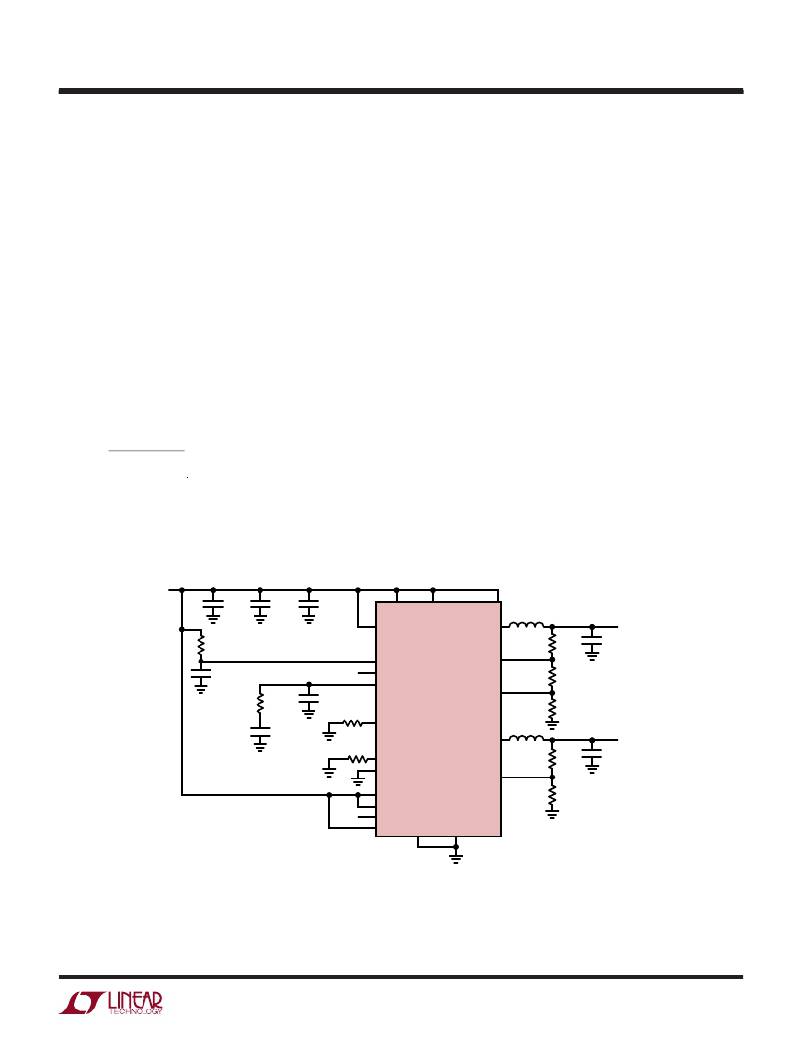

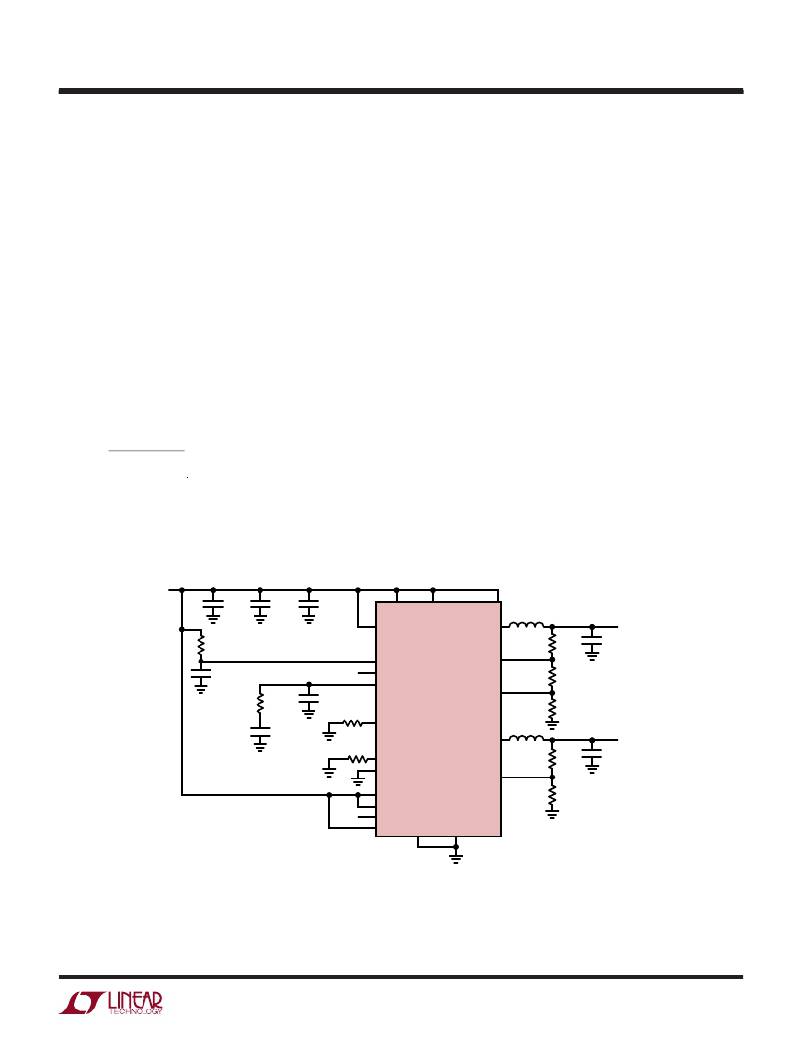

�TRACK/SS1�

�V� IN�

�3.3V�

�47μF�

�R� SS�

�4.7M�

�C� SS�

�10nF�

�47μF�

�R� C�

�15k�

�C� C�

�1000pF�

�1μF�

�10pF�

�R� T� ,� 200k�

�R� SRLIM�

�40.2k�

�SV� IN� (2� � )� PV� IN1� (2� � )� PV� IN2�

�RUN1� (2� � )� SW1�

�FB1�

�PGOOD1�

�ITH1�

�LTC3615� MODE�

�R� T� /SYNC�

�(2� � )� SW2�

�SRLIM�

�PHASE�

�FB2�

�0.47μH�

�0.47μH�

�R1�

�422k�

�R2�

�29.4k�

�R3�

�178k�

�R5�

�665k�

�V� OUT1�

�1.8V/3A�

�47μF�

�V� OUT2�

�2.5V/3A�

�47μF�

�RUN2�

�TRACK/SS2�

�PGOOD2�

�ITH2� SGND�

�PGND�

�R4�

�210k�

�3615� F03�

�Figure� 3.� Soft-Start� and� Compensation� for� Channel� 1� Externally� Programmed,�

�Soft-Start� and� Compensation� for� Channel� 2� Internally� Programmed�

�15�

�For� more� information� www.linear.com/LTC3615�

�3615fb�

�相关PDF资料 |

PDF描述 |

|---|---|

| RBC25DCAD | CONN EDGECARD 50POS R/A .100 SLD |

| RBB05DHFR | CONN EDGECARD 10POS .050 SMD |

| LTC3615EUF-1#PBF | IC REG BUCK SYNC ADJ 3A DL 24QFN |

| MAX6423US24+T | IC MPU/RESET CIRC 2.40V SOT143-4 |

| LT1076CR#PBF | IC REG MULTI CONFIG ADJ 2A D2PAK |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC3615HFE#PBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HFE#TRPBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HFE-1#PBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HFE-1#TRPBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

| LTC3615HUF#PBF | 制造商:Linear Technology 功能描述:IC REG BUCK SYNC ADJ 3A 24TSSOP |

发布紧急采购,3分钟左右您将得到回复。