- 您现在的位置:买卖IC网 > PDF目录383307 > MA31750 (Dynex Semiconductor Ltd.) High Performance MIL-STD-1750 Microprocessor PDF资料下载

参数资料

| 型号: | MA31750 |

| 厂商: | Dynex Semiconductor Ltd. |

| 英文描述: | High Performance MIL-STD-1750 Microprocessor |

| 中文描述: | 高性能的MIL - STD - 1750微处理器 |

| 文件页数: | 11/42页 |

| 文件大小: | 436K |

| 代理商: | MA31750 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

MA31750

11/42

4.8. MIL-STD-1750 DATA TYPES

The MA31750 fully supports 16-bit fixed-point single-

precision, 32-bit fixed-point double-precision, 32-bit floating-

point, and 48-bit extended precision floating- point data types.

Figure 16 depicts the formats of these data types.

All numerical data is represented in two’s complement

form. Floating-point numbers are represented by a fractional

two’s complement mantissa with an 8-bit two’s complement

exponent. All floating-point operands are expected to be

normalised. If not normalised, the results from an instruction

are not defined.

4.9. MIL-STD-1750 ADDRESSING MODES

The MA31750 supports the eight basic addressing modes

specified in MIL-STD-1750A. These addressing modes are

depicted in Figure 18 and are defined below. In binary

operations one operand is assumed to be in a register

(specified as part of the opcode) whilst the second operand

(the Derived Operand, DO) is taken from a source which is

dependent upon the addressing mode, see figure 17. Many

adddressing modes may be specified as indexable: the index

register may be any of the general purpose registers R1-R15

(if 0 is specified then the non-indexable form is used). For

Base Relative addressing modes the first operand is fixed as

part of the instruction (either R0 for Double Integer operations,

or R2 for Single Integer operations).

4.10. MEMORY ADDRESSING CAPABILITY

In accordance with MIL-STD-1750A, the MA31750 can

access a 64KWord address space directly. With the addition of

a single external Dynex Semiconductor MA31751 chip,

configured as a Memory Management Unit (MMU), this

address space may be expanded to 1MWord (1750A mode) or

8MWord (1750B mode). The MA31751 data sheet gives

further information on the MMU/BPU chip and on the memory

management scheme employed. Note that whilst one MMU

can be used to provide the full range of physical addresses to

the system memory, the logical addressing capability may also

be expanded by adding further MMU devices up to a maximum

of 16.

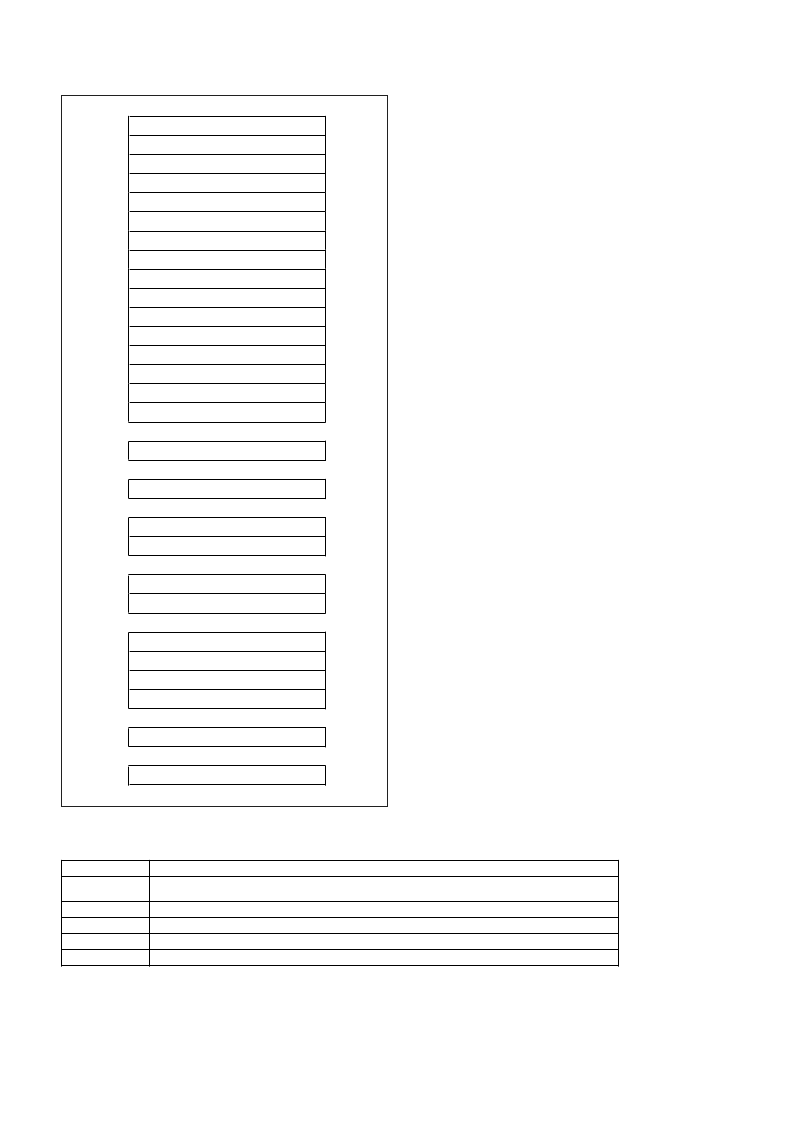

Figure 14: Register Set Model

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15

Status Word (SW)

Instruction Counter (IC)

Fault Register (FT)

Fault Mask (1750B only)

Pending Interrupt (PI)

Interrupt Mask (MK)

Timer A

Timer A reset (1750B only)

Timer B

Timer B reset (1750B only)

Trigger-Go Reset Register

Configuration

Register(s)

R0

Notional Use or Restriction on Use

Cannot be used as an index register

With R1: Implied register in Double mode Base Relative addressing

Implied register in Single mode Base Relative addressing

General purpose

Base relative registers

Stack pointer in PSHM and POPM operations

R2

R3-R11

R12-R15

R15

Figure 15: General Register Usage

相关PDF资料 |

PDF描述 |

|---|---|

| MA31751 | Memory Management & Block Protection Unit |

| MA31753 | DMA Controller (DMAC) For An MA31750 System |

| MA31755 | 16-Bit Feedthrough Error Detection & Correction Unit EDAC |

| MA3690 | 1553B Bus Controller/Remote Terminal |

| MA3691 | 1553B Bus Controller/Remote Terminal |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MA31751 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:Memory Management & Block Protection Unit |

| MA31753 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:DMA Controller (DMAC) For An MA31750 System |

| MA31755 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:16-Bit Feedthrough Error Detection & Correction Unit EDAC |

| MA318 | 功能描述:CPU与芯片冷却器 INTEL P111 FC-PGA RoHS:否 制造商:ADLINK Technology 尺寸: 电压额定值: 功率额定值: 速度: 气流: 系列: |

| MA3180 | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Silicon planar type |

发布紧急采购,3分钟左右您将得到回复。