- 您现在的位置:买卖IC网 > PDF目录383307 > MA31750 (Dynex Semiconductor Ltd.) High Performance MIL-STD-1750 Microprocessor PDF资料下载

参数资料

| 型号: | MA31750 |

| 厂商: | Dynex Semiconductor Ltd. |

| 英文描述: | High Performance MIL-STD-1750 Microprocessor |

| 中文描述: | 高性能的MIL - STD - 1750微处理器 |

| 文件页数: | 36/42页 |

| 文件大小: | 436K |

| 代理商: | MA31750 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页当前第36页第37页第38页第39页第40页第41页第42页

MA31750

36/42

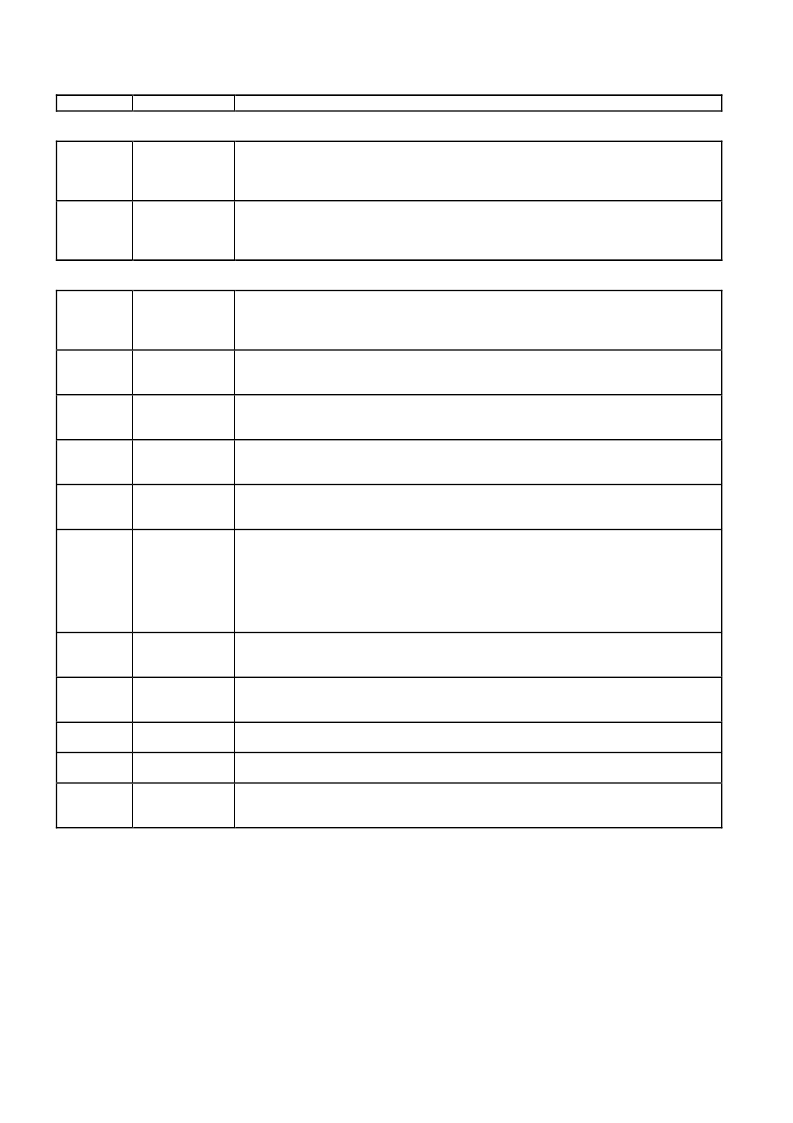

Pin Name

Function

Description

MMU CONTROL

AS[0:3]

Address State

Active HIGH

AS0 is MSB

This active-high bus indicates the current address state of the CPU. The value on this bus

is copied from the Status Word register within the CPU. These lines are inputs during bus

cycles not assigned to this CPU, so that the MFPR and the MFAR can store the relevant

failure information if a remote failure occurs.

In 1750B mode, this active-high bus indicates the current CPU Page Bank. The value on

this bus is copied from the Status Word register within the CPU. These lines are inputs

during bus cycles not assigned to this CPU, so that the MFPR and the MFAR can store the

relevant failure information if a remote failure occurs.

PB[0:3]

Page Bank Select

Active HIGH

PB0 is MSB

DISCRETES

CONFWN

Configuration

Register Read

Strobe

Active LOW

Start of New

Cycle Strobe

Active HIGH

Discretes Output

Strobe

Active LOW

DMA Enable

Active HIGH

This active-low output signal is driven low when the processor reads the external

configuration register. The line may be used as an output enable for this register. The

configuration register is read during initialisation and during the execution of a BPT

instruction to determine the system configuration.

This active-high output will be asserted high during the first phase of each machine cycle.

SNEW

DISCON

This active-low output will be asserted low by the processor during an XIO OD or XIO RDOR

command. It may be used as the enable signal for an external discrete output register.

DMAE

This active-high output indicates that an external DMA device is enabled. It is disabled

(low) following reset and can be toggled under program control using XIO DMAE and XIO

DMAD, (if a DMA device is set as present in the configuration register).

This active-low input initiates and controls Console operation following the end of a 1750

instruction. Commands and data are passed to the processor in this mode via three

dedicated registers in IO space. Console operation takes precedence over Interrupts.

This active-low output indicates that start-up ROM is enabled. The signal is asserted low

following initialisation or by XIO ESUR. The signal remains asserted until removed with XIO

DSUR. When a start-up ROM is present on the system indicated in the configuration word,

this signal should be used to qualify its chip select or output enable such that the ROM

may be accessed only when SUREN is low.

Note:

Instruction pipelining must be considered in moving from Start-Up ROM to RAM.

See Section 4 on Software Considerations.

This output is asserted to indicate that the Built-ln-Test (BIT), performed on reset or power-

up, has passed. The line is asserted low following an external reset and may also be reset

by software using the XIO RNS command.

This active-low output is asserted low whenever the Trigger-Go counter overflows (rolls

over to 0000). It returns to the high state when the counter is reset by software (using the

XIO GO command).

A low on this input will reset and disable the bus fault timeout circuit.

CONREQN

Console Request

Active LOW

SUREN

Start-Up-ROM

Enable

Active LOW

NPU

Normal Power-Up

Discrete

Active HIGH

Trigger-Go Output

Discrete

Active LOW

Disable Timeout

Active LOW

Disable Parity

Active LOW

CPU reset

Reset=LOW

TGON

DTON

DPARN

A low on this input will reset and disable the on-chip parity verification.

Note:

Parity generationon write data is not disabled by this pin.

This active-low input should be asserted low to reset the processor. The low to high

transition will start the initialisation sequence which will perform a Built-In-Test (if

selected), initialising the processor in accordance with MIL-STD-1750 (see figures 2 and 3).

RESETN

Figure 39 (continued): Pin Descriptions

相关PDF资料 |

PDF描述 |

|---|---|

| MA31751 | Memory Management & Block Protection Unit |

| MA31753 | DMA Controller (DMAC) For An MA31750 System |

| MA31755 | 16-Bit Feedthrough Error Detection & Correction Unit EDAC |

| MA3690 | 1553B Bus Controller/Remote Terminal |

| MA3691 | 1553B Bus Controller/Remote Terminal |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MA31751 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:Memory Management & Block Protection Unit |

| MA31753 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:DMA Controller (DMAC) For An MA31750 System |

| MA31755 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:16-Bit Feedthrough Error Detection & Correction Unit EDAC |

| MA318 | 功能描述:CPU与芯片冷却器 INTEL P111 FC-PGA RoHS:否 制造商:ADLINK Technology 尺寸: 电压额定值: 功率额定值: 速度: 气流: 系列: |

| MA3180 | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Silicon planar type |

发布紧急采购,3分钟左右您将得到回复。