- 您现在的位置:买卖IC网 > PDF目录383307 > MA31750 (Dynex Semiconductor Ltd.) High Performance MIL-STD-1750 Microprocessor PDF资料下载

参数资料

| 型号: | MA31750 |

| 厂商: | Dynex Semiconductor Ltd. |

| 英文描述: | High Performance MIL-STD-1750 Microprocessor |

| 中文描述: | 高性能的MIL - STD - 1750微处理器 |

| 文件页数: | 5/42页 |

| 文件大小: | 436K |

| 代理商: | MA31750 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页

MA31750

5/42

3.2. INSTRUCTION EXECUTION

Once initialisation has been completed, the processor will

begin instruction execution. Instruction execution is

characterised by a variety of operations, each is one machine

cycle in duration (two or more system CLK periods).

Depending on the instruction being executed at the time, these

operations include: (1) internal CPU cycles, (2) instruction

fetches, (3) operand transfers, and (4) input/output transfers.

Instruction execution may be interrupted at the end of any

individual machine cycle by an interrupt or Console request.

Internal cycles are always two CLK periods long, whilst the

other cycle types are a minimum of two CLK periods -

extendable by inserting waitstates. In all cycles except internal

cycles, RDN, WRN, DSN and AS strobes are produced to

control the transfer and latching of data and address around

the system.

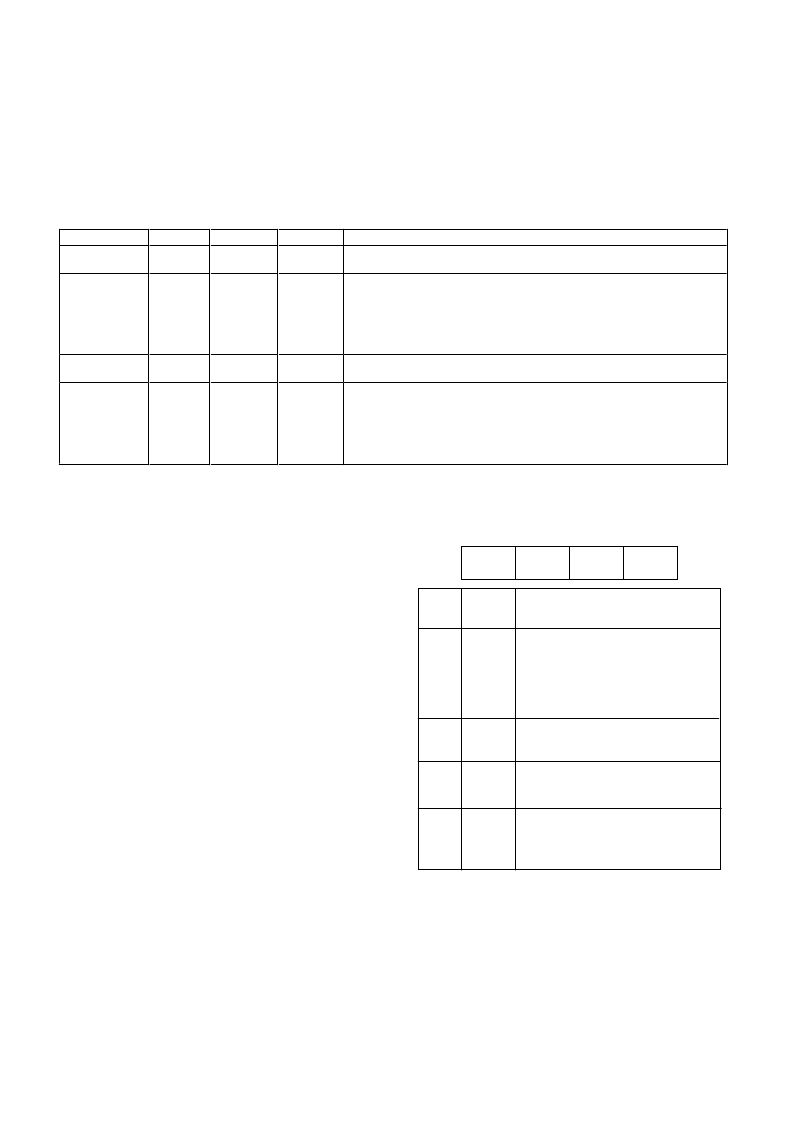

Cycle Type

Internal Cycle

RD/WRN

H

O/IN

L

M/ION

H

Description

Used to perform all CPU data manipulation operations where bus

activity is not required.

Used to keep the instruction pipeline full with instructions and/or their

postwords. At least one instruction is always ready for execution when

the preceding instruction is completed. During jump and branch

instruction execution the pipeline is refilled by two consecutive

instruction fetches starting at the new instruction location. It is also

refilled as part of interrupt request processing.

Used to read in data from the external system and to write results to the

system.

Input/Output transfers utilize the MIL-STD-1750 XIO and VIO

instructions. RD/WN defines the direction of the transfer. IO transfers

may be divided into three groups; those commands which are

implemented internally by the CPU, those commands which are

implemented by external system hardware and those commands

defined as illegal by MIL-STD-1750A and B.

Instruction

Fetch

H

L

H

Operand Read

Operand Write

IO Read

IO Write

H

L

H

L

H

H

H

H

H

H

L

L

Figure 7: External Cycle Types

3.3. IO OPERATION

The MA31750 supports a 64KWord addressing space

dedicated to IO control and communication in accordance with

MIL-STD-1750. The control line MION is asserted low when

accessing IO space (see figure 7 above for other strobe

states). One of the two commands XIO or VIO is used to

specify both data for the transfer and the port address (referred

to as an XIO Command in 1750). The CPU contains logic

which decodes all internally supported XIO commands and

generates the control signals necessary to carry out the

commanded action. In addition, the validity of a command not

implemented internally is verified. Figure 20c identifies the XIO

commands which are internally supported by the MA31750.

3.4. INTERRUPT AND FAULT HANDLING

3.4.1. STATUS WORD (SW)

Figure 8 depicts the status register format. This 16-bit word

is divided into four, 4-bit sections. Three of these sections [AS,

PS and, (1750B mode) PB] are control bits for implementing

expanded memory with an external MMU. The fourth section,

CS, is used to hold the carry, positive, zero and negative

condition flags set by the result of the previous arithmetic

operation.

CS

R (PB)

PS

AS

0

3 4

7 8

11 12

15

Field

Bits

Description

CS

0

1

2

3

CONDITION STATUS

C- Carry from an addition or no

borrow from a subtraction.

P- Result > 0

Z- Result = 0

N- Result < 0

R

PB

4-7

RESERVED (=0) in 1750A mode

Page Bank Select in 1750B mode

PS

8-11

PROCESSOR STATE:

(a)- Memory access to key code

(b)- Priviledged instruction enable

AS

12-15

ADDRESS STATE:

Page register sets for expanded

memory addressing.

Figure 8: Status Word Format

相关PDF资料 |

PDF描述 |

|---|---|

| MA31751 | Memory Management & Block Protection Unit |

| MA31753 | DMA Controller (DMAC) For An MA31750 System |

| MA31755 | 16-Bit Feedthrough Error Detection & Correction Unit EDAC |

| MA3690 | 1553B Bus Controller/Remote Terminal |

| MA3691 | 1553B Bus Controller/Remote Terminal |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MA31751 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:Memory Management & Block Protection Unit |

| MA31753 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:DMA Controller (DMAC) For An MA31750 System |

| MA31755 | 制造商:DYNEX 制造商全称:Dynex Semiconductor 功能描述:16-Bit Feedthrough Error Detection & Correction Unit EDAC |

| MA318 | 功能描述:CPU与芯片冷却器 INTEL P111 FC-PGA RoHS:否 制造商:ADLINK Technology 尺寸: 电压额定值: 功率额定值: 速度: 气流: 系列: |

| MA3180 | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Silicon planar type |

发布紧急采购,3分钟左右您将得到回复。