- 您现在的位置:买卖IC网 > PDF目录69032 > MCF54418CMJ250 (FREESCALE SEMICONDUCTOR INC) MICROPROCESSOR, PBGA256 PDF资料下载

参数资料

| 型号: | MCF54418CMJ250 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | MICROPROCESSOR, PBGA256 |

| 封装: | 12 X 12 MM, ROHS COMPLAINT, MAPBGA-256 |

| 文件页数: | 41/60页 |

| 文件大小: | 1107K |

| 代理商: | MCF54418CMJ250 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 6

Preliminary—Subject to Change Without Notice

Electrical characteristics

Freescale Semiconductor

46

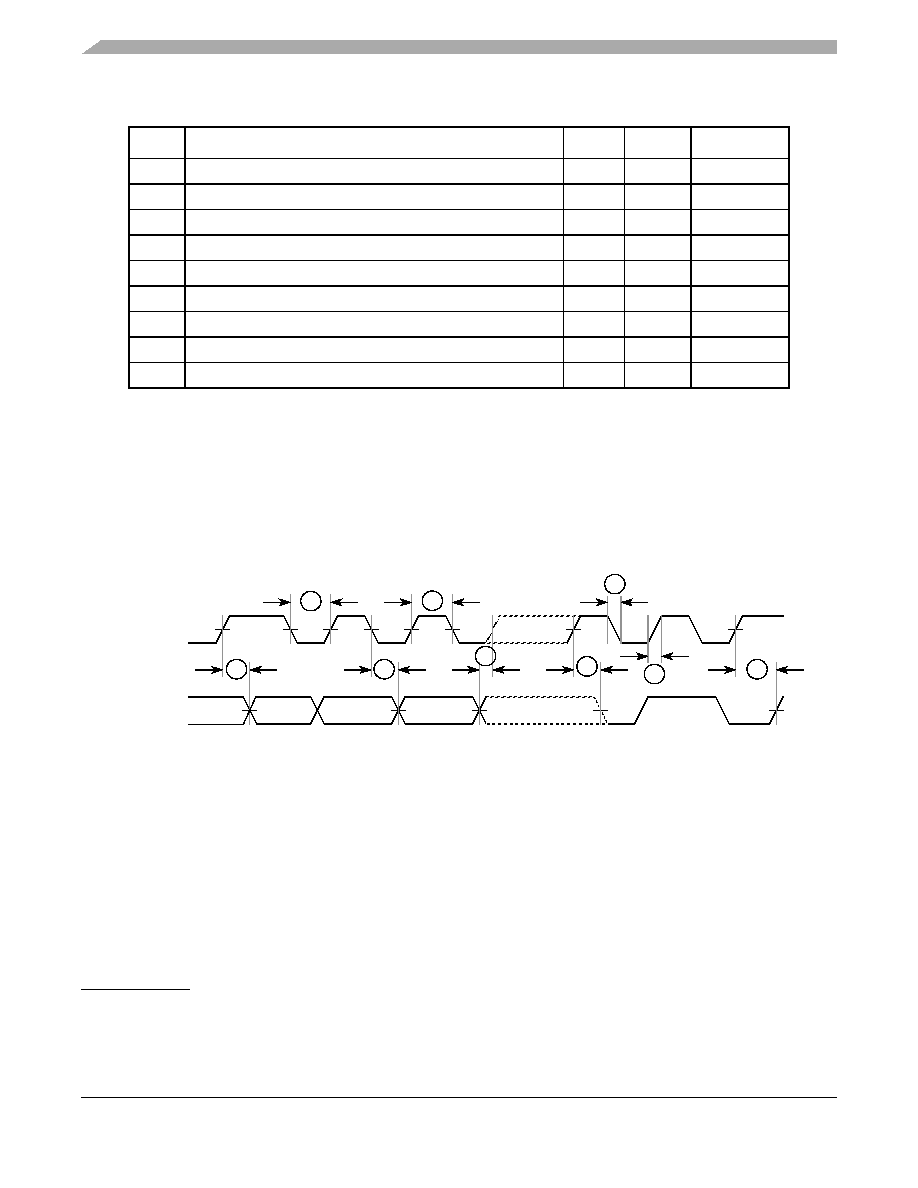

Figure 27. I2C input/output timings

4.22

Ethernet assembly timing specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing

specs/constraints for the physical interface.

All Ethernet signals use pad type pad_fsr. The following timing specifications assume a pad slew rate setting of 11 and a load

of 50 pF.1

Table 30. I2C output timing specifications between SCL and SDA

Num

Characteristic

Min

Max

Units

I11

1 Output numbers depend on the value programmed into the IFDR; an IFDR programmed with the maximum

frequency (IFDR = 0x20) results in minimum output timings as shown in Table 30. The I2C interface is

designed to scale the actual data transition time to move it to the middle of the SCL low period. The actual

position is affected by the prescale and division values programmed into the IFDR. However, the numbers

given in Table 30 are minimum values.

Start condition hold time

6

—

1/fSYS

I21

Clock low period

10

—

1/fSYS

I32

2 Because I2C_SCL and I2C_SDA are open-collector-type outputs, which the processor can only actively drive

low, the time I2C_SCL or I2C_SDA take to reach a high level depends on external signal capacitance and

pull-up resistor values.

I2C_SCL/I2C_SDA rise time (VIL = 0.5 V to VIH =2.4 V)

—

s

I41

Data hold time

7

—

1/fSYS

I53

3 Specified at a nominal 50-pF load.

I2C_SCL/I2C_SDA fall time (VIH = 2.4 V to VIL = 0.5 V)

—

3

ns

I61

Clock high time

10

—

1/fSYS

I71

Data setup time

2

—

1/fSYS

I81

Start condition setup time (for repeated start condition only)

20

—

1/fSYS

I91

Stop condition setup time

10

—

1/fSYS

1.These timing parameters are specified assuming maximum operating frequency and the fastest pad slew rate setting

(11). When operating this interface at lower frequencies, increase the slew rate by using the 10, 01, or 00 setting to

increase edge rise and fall times, thus reducing EMI.

I2

I6

I1

I4

I7

I8

I9

I5

I3

I2C_SCL

I2C_SDA

相关PDF资料 |

PDF描述 |

|---|---|

| MCF54415CMJ250 | MICROPROCESSOR, PBGA256 |

| MCIMX251AJM4A | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA400 |

| MCIMX255AJM4 | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA400 |

| MCIMX251AVM4 | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA400 |

| MCIMX27VOP4 | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA404 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MCF54418CMJ250 | 制造商:Freescale Semiconductor 功能描述:IC 32-BIT MPU COLDFIRE 250MHZ 256-MA |

| MCF5441X | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:MCF5441x ColdFire Microprocessor Data Sheet |

| MCF54450 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:ColdFire㈢ Microprocessor |

| MCF54450ACVM180 | 制造商:Freescale Semiconductor 功能描述:MCF5445X RISC 32-BIT 180MHZ 1.8V/2.5V/3.3V 256-PIN MA-BGA BR - Trays 制造商:Freescale Semiconductor 功能描述:MCF5445X V4M CORE, MMU, 制造商:Freescale 功能描述:MPU MCF5445X RISC 32-Bit 180MHz 1.8V/2.5V/3.3V 256-Pin MAP-BGA Brick |

| MCF54450AVM240 | 制造商:Freescale Semiconductor 功能描述:MCF5445X RISC 32-BIT 240MHZ 1.8V/2.5V/3.3V 256-PIN MA-BGA BR - Trays |

发布紧急采购,3分钟左右您将得到回复。