- 您现在的位置:买卖IC网 > PDF目录69037 > MSC8101VT1250F (FREESCALE SEMICONDUCTOR INC) 64-BIT, 62.5 MHz, OTHER DSP, PBGA332 PDF资料下载

参数资料

| 型号: | MSC8101VT1250F |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 64-BIT, 62.5 MHz, OTHER DSP, PBGA332 |

| 封装: | 17 X 17 MM, LIDDED FLIP CHIP, PLASTIC, BGA-332 |

| 文件页数: | 94/104页 |

| 文件大小: | 1811K |

| 代理商: | MSC8101VT1250F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页当前第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

Reset, Configuration, and EOnCE Event Signals

MSC8101 Technical Data, Rev. 18

Freescale Semiconductor

1-5

1.3 Reset, Configuration, and EOnCE Event Signals

CLKOUT

Output

Clock Out

The system bus clock.

DLLIN

Input

DLLIN

Synchronizes with an external device.

Note:

When the DLL is disabled, connect this signal to GND.

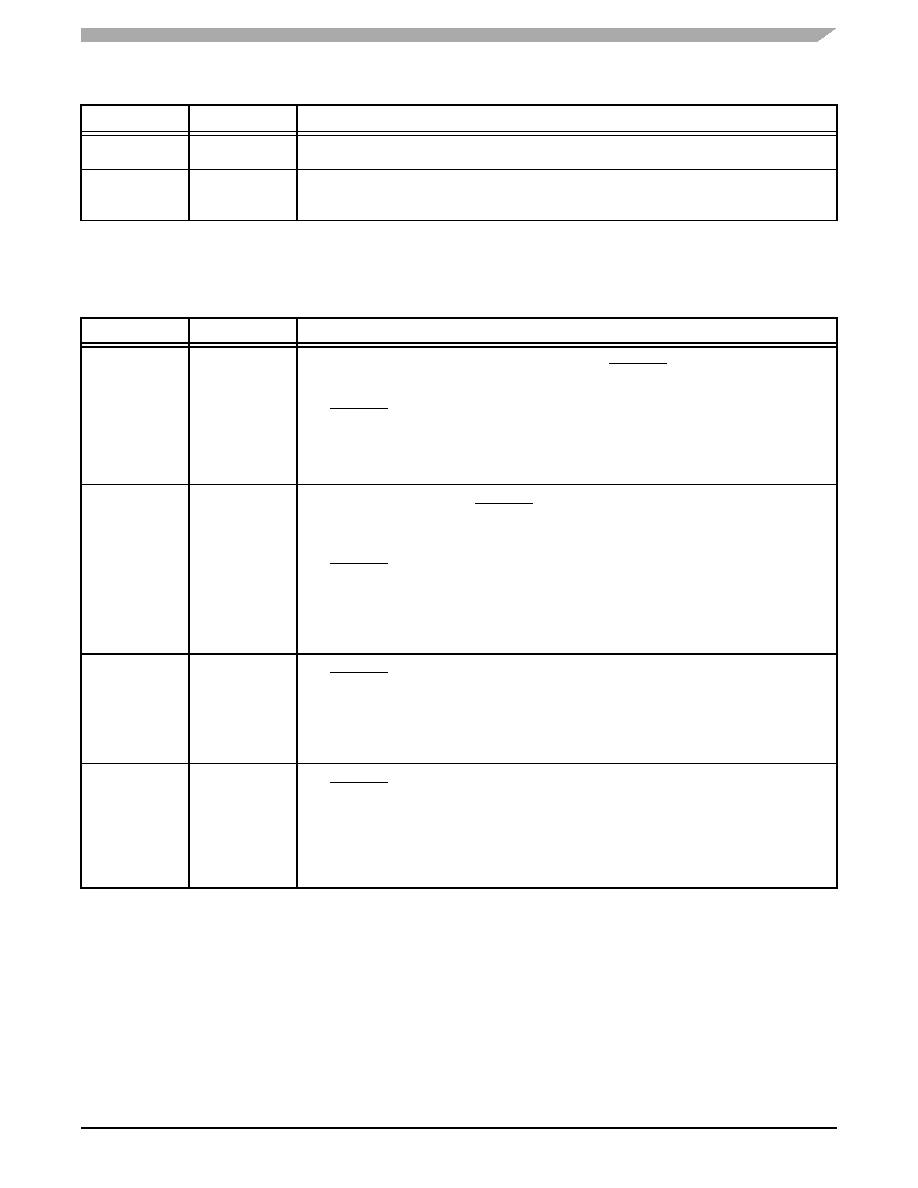

Table 1-4.

Reset, Configuration, and EOnCE Event Signals

Signal Name

Type

Signal Description

DBREQ

EE01

Input

Output

Debug Request

Determines whether to go into SC140 Debug mode when PORESET is deasserted.

Enhanced OnCE (EOnCE) Event 0

After PORESET is deasserted, you can configure EE0 as an input (default) or an output.

Debug request, enable Address Event Detection Channel 0, or generate an EOnCE event.

Detection by Address Event Detection Channel 0. Used to trigger external debugging equipment.

HPE

EE11

Input

Output

Host Port Enable

When this pin is asserted during PORESET, the Host port is enabled, the system data bus is 32 bits

wide, and the Host

must program the reset configuration word.

EOnCE Event 1

After PORESET is deasserted, you can configure EE1 as an input (default) or an output.

Enable Address Event Detection Channel 1 or generate an EOnCE event.

Debug Acknowledge or detection by Address Event Detection Channel 1. Used to trigger external

debugging equipment.

EE21

Input

Output

EOnCE Event 2

After PORESET is deasserted, you can configure EE2 as an input (default) or an output.

Enable Address Event Detection Channel 2 or generate an EOnCE event or enable the Event

Counter.

Detection by Address Event Detection Channel 2. Used to trigger external debugging equipment.

EE31

Input

Output

EOnCE Event 3

After PORESET is deasserted, you can configure EE3 as an input (default) or an output. See the

emulation and debug chapter in the

SC140 DSP Core Reference Manual for details on the ERCV

Register.

Enable Address Event Detection Channel 3 or generate one of the EOnCE events.

The DSP has read the EOnCE Receive Register (ERCV). Triggers external debugging equipment.

Table 1-3.

Clock Signals (Continued)

Signal Name

Type

Signal Description

相关PDF资料 |

PDF描述 |

|---|---|

| MSC8101VT1500F | 64-BIT, 75 MHz, OTHER DSP, PBGA332 |

| MSC8101M1375F | 64-BIT, 68.75 MHz, OTHER DSP, PBGA332 |

| MSC8126VT8000 | 0-BIT, 500 MHz, OTHER DSP, PBGA431 |

| MSC8126TMP6400 | 0-BIT, 400 MHz, OTHER DSP, PBGA431 |

| MSM5055 | 4-BIT, MROM, 0.032768 MHz, MICROCONTROLLER, UUC94 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MSC8101VT1375F | 功能描述:IC DSP 16BIT 250MHZ 332-FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| MSC8101VT1500F | 功能描述:IC DSP 16BIT 250MHZ 332-FCPBGA RoHS:是 类别:集成电路 (IC) >> 嵌入式 - DSP(数字式信号处理器) 系列:StarCore 标准包装:2 系列:StarCore 类型:SC140 内核 接口:DSI,以太网,RS-232 时钟速率:400MHz 非易失内存:外部 芯片上RAM:1.436MB 电压 - 输入/输出:3.30V 电压 - 核心:1.20V 工作温度:-40°C ~ 105°C 安装类型:表面贴装 封装/外壳:431-BFBGA,FCBGA 供应商设备封装:431-FCPBGA(20x20) 包装:托盘 |

| MSC8102 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Quad Core 16-Bit Digital Signal Processor |

| MSC81020 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS GENERAL PURPOSE AMPLIFIER APPLICATIONS |

| MSC8102M4000 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Quad Core 16-Bit Digital Signal Processor |

发布紧急采购,3分钟左右您将得到回复。