- 您现在的位置:买卖IC网 > PDF目录224505 > MT41J512M4JE-187EIT:A 64M X 4 DDR DRAM, PBGA82 PDF资料下载

参数资料

| 型号: | MT41J512M4JE-187EIT:A |

| 元件分类: | DRAM |

| 英文描述: | 64M X 4 DDR DRAM, PBGA82 |

| 封装: | 12.50 X 15 MM, LEAD FREE, FBGA-82 |

| 文件页数: | 11/11页 |

| 文件大小: | 288K |

PDF: 09005aef826aaadc/Source: 09005aef826a65af

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2Gb DDR3 SDRAM.fm - Rev. C 12/07 EN

9

2006 Micron Technology, Inc. All rights reserved.

2Gb: x4, x8 DDR3 SDRAM

Mode Register (MR) Definition

Advance

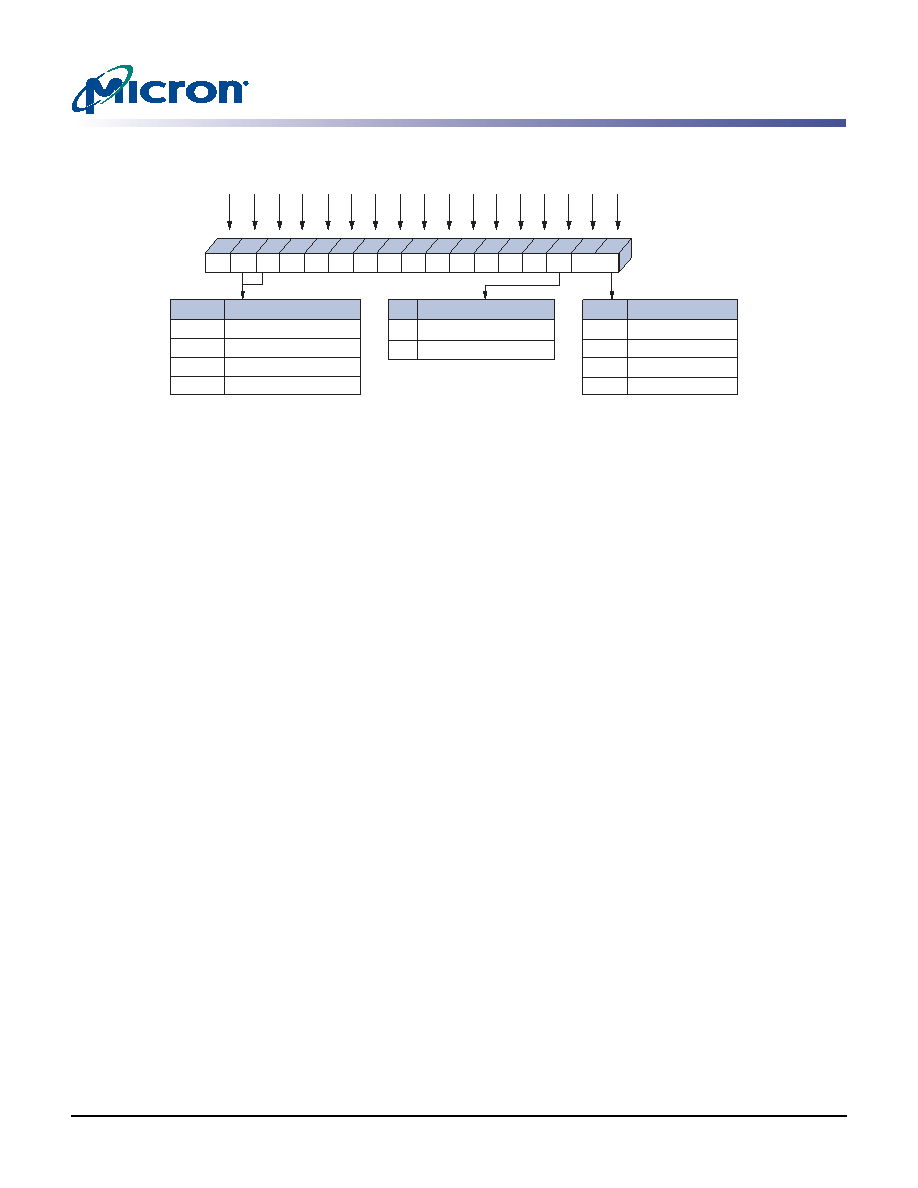

Figure 6:

Mode Register 3 (MR3) Definition

Notes:

1. MR3[16, 13:4] are reserved for future use and must all be programmed to “0.”

2. When MPR control is set for normal DRAM operation, MR3[1,0] will be ignored.

3. Intended to be used for READ synchronization.

A9

A7

A6 A5

A4 A3

A8

A2

A1

A0

Mode register 3 (MR3)

Address bus

97

6

54

3

8

2

1

0

A10

A12 A11

BA0

BA1

10

11

12

13

14

15

A13

101 01

01 01 01

01

MPR

1

BA2

16

01

M2

0

1

MPR Enable

Normal DRAM operations2

Dataflow from MPR

MPR_RF

M14

0

1

0

1

M15

0

1

Mode Register

Mode register set (MR0)

Mode register set 1 (MR1)

Mode register set 2 (MR2)

Mode register set 3 (MR3)

MPR READ Function

Predefined pattern3

Reserved

M0

0

1

0

1

M1

0

1

相关PDF资料 |

PDF描述 |

|---|---|

| MT42C8255RG-7TR | 256K X 8 VIDEO DRAM, 70 ns, PDSO40 |

| MT46V32M16TG-75ELIT | 32M X 16 DDR DRAM, 0.75 ns, PDSO66 |

| MT46V32M16BN-5BLIT | 32M X 16 DDR DRAM, 0.7 ns, PBGA60 |

| MT46V32M81AZ4-6T:G | 32M X 4 DDR DRAM, 0.75 ns, PDSO66 |

| MT47H128M8HV-187ELIT:E | 128M X 8 DDR DRAM, 0.35 ns, PBGA60 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT41J512M4V79D3WC1 | 制造商:Micron Technology Inc 功能描述:512MX4 DDR3 SDRAM DIE-COM COMMERCIAL 1.5V - Trays |

| MT41J512M4V89C3WC1 | 制造商:Micron Technology Inc 功能描述:512MX4 DDR3 SDRAM DIE-COM COMMERCIAL 1.5V - Bulk |

发布紧急采购,3分钟左右您将得到回复。