- 您现在的位置:买卖IC网 > PDF目录296691 > NHI-1598ET/883 (NATIONAL HYBRID INC) 2 CHANNEL(S), MIL-STD-1553 CONTROLLER, CPGA69 PDF资料下载

参数资料

| 型号: | NHI-1598ET/883 |

| 厂商: | NATIONAL HYBRID INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 2 CHANNEL(S), MIL-STD-1553 CONTROLLER, CPGA69 |

| 封装: | 1.100 X 1.100 INCH, CERAMIC, PLUG IN, PGA-69 |

| 文件页数: | 17/89页 |

| 文件大小: | 569K |

| 代理商: | NHI-1598ET/883 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页

-

23

4.2.14

LAST STATUS REGISTER

Address: 12

R

RT

This register holds the Status Word assosciated with the last message. After initialization of the

RT, the BUSY bit= 1, the TADR field contains the hardwire address, and all other bits are set to

0.

See RTC CONTROL REGISTER for special options.

4.2.15

RESET REMOTE TERMINAL

Address: 15

W

BC/ MT/ RT

Writing a word to address 15 resets the RT and causes it to perform its initialization (see

initialization section).

4.2.16

ENCODER STATUS

Address: 18

R

BC/ RT

This register contains flags indicating the status of the encoder. These flags are intended to

facilitate transmission of messages in loop- back mode during self- test.

15

7

0

TXREQ_L

EOTX_L

FAILSAFE_L

TXREQ_ L

Bits: 15

RT

0= Indicates that the encoder is ready to accept the next word for transmission. This bit should

equal "0" before loading the Encoder Data register with the next word. In order to transmit

contiguous words, the next word should be loaded within 18 microseconds after *TXREQ

transitions to "0".

EOTX_ L

Bits: 7

RT

0= Indicates that the encoder has completed transmission and that there are no pending

requests.

FAILSAFE_ L

Bits: 0

BC/ RT

0= FAILSAFE TIME OUT has occurred. This bit will be set to a "1" when a new message is

received or during a reset.

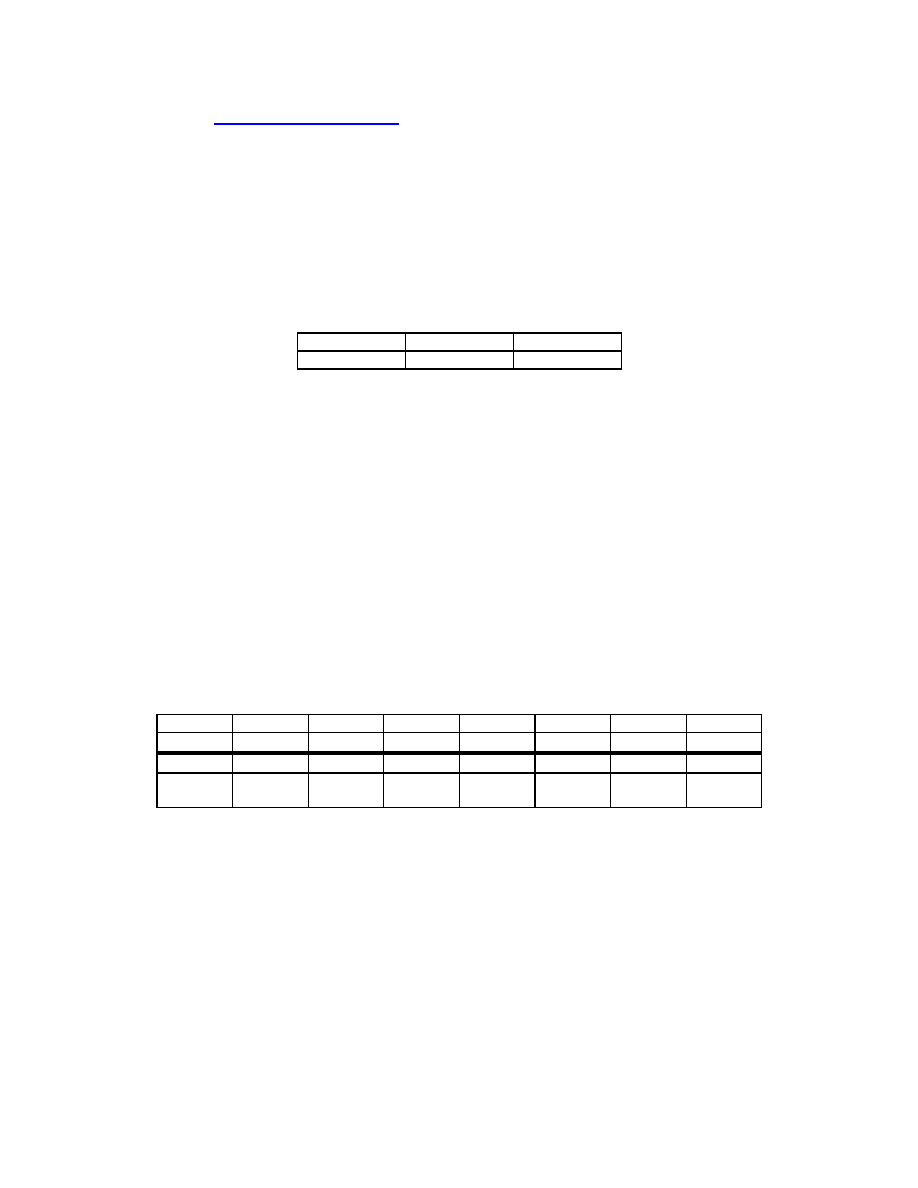

4.2.17

CONDITION REGISTER

Address: 19

R

BC/ MT/ RT

This register contains information about the command being processed by the NHi- ET. and the

operational condition.of the NHi-ET.

15

14

13

12

11

10

9

8

X

AXEN

BXEN

TFE

X

MDCD_L

X

7

6

5

4

3

2

1

0

X

CUFRM

BUSY

EOF B

EOF A

CUR

FRM

CUR

BUS

BUSJAM

B

BUSJAM

A

AXEN

Bits: 13

BC/ RT

1= Indicates that transmitter A is enabled. This bit is set to a "1": at POWER UP, if the NHi- ET is

RESET, after receipt of a "Reset" mode code, or after receipt of an OVERRIDE

TRANSMITTER SHUTDOWN mode code on the B bus.

0= Indicates that transmitter A is inhibited. This bit is set to a "0" after receipt of TRANSMITTER

SHUTDOWN mode code on the B bus.

BXEN

Bits: 12

BC/ RT

1= Indicates that transmitter B is enabled. This bit is set to a "1": at POWER UP, if the NHi- ET is

RESET, after receipt of a "Reset" mode code, or after receipt of an OVERRIDE

TRANSMITTER SHUTDOWN mode code on the A bus.

0= Indicates that transmitter B is inhibited. This bit is set to a "0" after receipt of a

TRANSMITTER SHUTDOWN mode code on the A bus.

相关PDF资料 |

PDF描述 |

|---|---|

| NJG1145UA2 | 90 MHz - 2150 MHz RF/MICROWAVE WIDE BAND LOW POWER AMPLIFIER |

| NJG1515AVB2 | RF/MICROWAVE TRANSFER SWITCH |

| NJG1667MD7 | 1000 MHz - 2500 MHz RF/MICROWAVE SGL POLE FIVE THROW SWITCH, 0.8 dB INSERTION LOSS |

| NJU6319DC | 6.25 MHz, OTHER CLOCK GENERATOR, UUC6 |

| NJU6338BE | 17.5 MHz, OTHER CLOCK GENERATOR, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NHI21PKZ0 | 制造商:EATON MOELLER 功能描述:Contactor 制造商:EATON MOELLER 功能描述:CONTACTOR; Contact Configuration:3PST-2NO / SPST-NC; IP / NEMA Rating:IP20; No. of Poles:3 ;RoHS Compliant: Yes |

| NHI21-PKZ0 | 制造商:Moeller Electric Corporation 功能描述:Auxiliary Switch Nhi-Pkz0 |

| NHI21-PKZO | 制造商:EATON MOELLER 功能描述:CONTACT BLOCK 2NO+1NC |

| NHI350AM2 S LJ3S | 制造商:Intel 功能描述:Ethernet CTLR Single Chip 10Mbps/100Mbps/1000Mbps 3.3V 256-Pin BGA 制造商:Intel 功能描述:POWERVILLE, ETHERNET CONTROLLER I350-AM2 - Trays |

| NHI350AM2 S LJ3S | 制造商:Intel 功能描述:Ethernet ICs Controller IEEE 10/ 100/1000 Mbps BGA256 |

发布紧急采购,3分钟左右您将得到回复。