参数资料

| 型号: | OPENLPPOL-EVB |

| 厂商: | Silicon Laboratories Inc |

| 文件页数: | 17/36页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL OPEN-LOOP POL |

| 标准包装: | 1 |

| 主要目的: | 电源管理,电流感应 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | Si8410,Si8512,Si8540 |

| 主要属性: | 单相 POL,100 ~ 500 kHz 切换频率 |

| 次要属性: | 20 ~ 80% 可变占空比 |

| 已供物品: | 板 |

| 产品目录页面: | 628 (CN2011-ZH PDF) |

| 其它名称: | 336-1919 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

�� �

�

Si85xx�

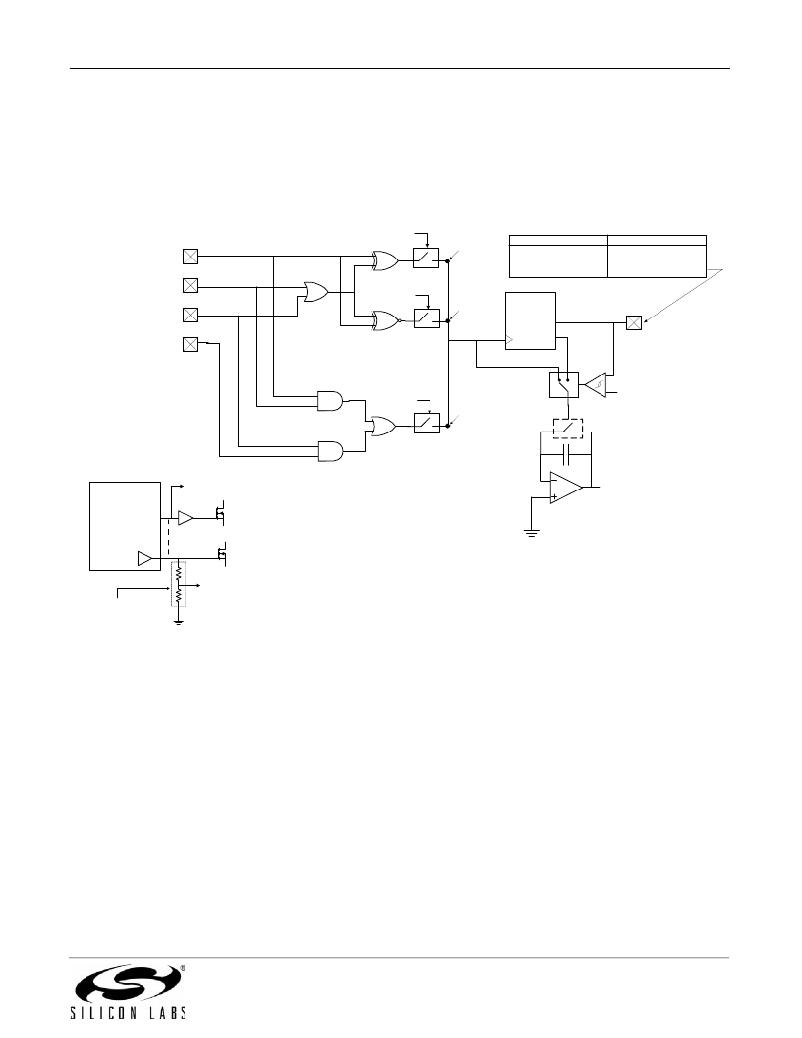

�As� explained� in� Section� “2.3.� Integrator� Reset� and� Current� Measurement”,� the� signals� applied� to� R1–R4� can�

�control� integrator� reset� in� real� time� (Option� 1),� or� they� can� trigger� a� reset� event� of� programmable� duration� (Option�

�2).� Referring� to� Figure� 14,� reset� timing� is� exclusively� a� function� of� the� signals� applied� to� R1–R4� when� TRST� is� tied�

�to� VDD.�

�If� not� connected� to� VDD,� the� reset� timer� is� enabled,� and� TRST� must� be� connected� through� a� resistor� to� ground� to�

�set� the� reset� duration� (t� R� ).� Note� that� the� reset� timer� is� retriggerable� and� generates� a� timed� integrator� discharge�

�pulse� whenever� the� reset� logic� output� transitions� from� low� to� high.�

�MODE� =� 1�

�R1�

�R2�

�R3�

�R4�

�R4� =� 0�

�MODE� =� 1�

�R4� =� 1�

�Output� 1�

�Output� 2�

�TRST� =� VDD�

�Reset� timing� determined�

�only� by� inputs� R1–R4.�

�RESET�

�TIMER�

�PGM�

�OUT�

�CLK�

�1�

�0�

�+�

�TRST� =� R1� to� GND�

�Reset� triggered� by� inputs�

�R1–R4.� Reset� time� (t� R� )� set�

�by� value� of� resistor� R� TRST� .�

�TRST�

�VREF�

�MODE� =� 0�

�Output� 3�

�Logic� level� gate�

�SYSTEM�

�CONTROLLER�

�control� signals�

�(to� Rn� inputs)�

�INTEGRATOR�

�External�

�Driver�

�Internal�

�Driver�

�Logic� level� gate�

�control� signals�

�Required� if� driver�

�(to� Rn� inputs)�

�output� voltage� >� VDD�

�Figure� 14.� Si851x� Integrator� Reset� Logic�

�Preliminary� Rev.� 0.4�

�17�

�相关PDF资料 |

PDF描述 |

|---|---|

| OVPL5W3K | KIT DESIGN POWER LINE WHITE |

| P0001 | MODULE DIGITAL CAMERA 5MP (D5M) |

| P0006 | BOARD ADAPTER THDB-SUM |

| P0307 | KIT DEV 4.3" LCD TOUCH PANEL |

| P0424 | KIT DEV 3.6" DIGITAL PANEL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OPEOPCK | 制造商:Eaton Corporation 功能描述:Ld Optim/Motor Operator - Optimizer Kit |

| OPERATIONMODE | 制造商:未知厂家 制造商全称:未知厂家 功能描述:EM73201/EM73E00/EM73PE00 Application Note |

| OPE-SRMINI | 制造商:Hitachi 功能描述:Bulk |

| OPEXM1S-W1 | 制造商:Black Box Corporation 功能描述:1 YEAR WARRANTY FOR OPEXM1S |

| OPEXM1S-W3 | 制造商:Black Box Corporation 功能描述:3 YEAR WARRANTY FOR OPEXM1S |

发布紧急采购,3分钟左右您将得到回复。