- 您现在的位置:买卖IC网 > PDF目录299575 > OR3T306S240I-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 196 CLBS, 48000 GATES, PQFP240 PDF资料下载

参数资料

| 型号: | OR3T306S240I-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 196 CLBS, 48000 GATES, PQFP240 |

| 封装: | PLASTIC, SQFP-240 |

| 文件页数: | 4/203页 |

| 文件大小: | 1368K |

| 代理商: | OR3T306S240I-DB |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页

Lattice Semiconductor

101

Data Sheet

November 2006

ORCA Series 3C and 3T FPGAs

Timing Characteristics

Description

To dene speed grades, the

ORCA Series part number

designation (see Ordering Information) uses a single-

digit number to designate a speed grade. This number

is not related to any single ac parameter. Higher num-

bers indicate a faster set of timing parameters. The

actual speed sorting is based on testing the delay in a

path consisting of an input buffer, combinatorial delay

through all PLCs in a row, and an output buffer. Other

tests are then done to verify other delay parameters,

such as routing delays, setup times to FFs, etc.

The most accurate timing characteristics are reported

by the timing analyzer in the ispLEVER Development

System. A timing report provided by the development

system after layout divides path delays into logic and

routing delays. The timing analyzer can also provide

logic delays prior to layout. While this allows routing

budget estimates, there is wide variance in routing

delays associated with different layouts.

The logic timing parameters noted in the Electrical

Characteristics section of this data sheet are the same

as those in the design tools. In the PFU timing given in

Table 41—Table 48, symbol names are generally a

concatenation of the PFU operating mode (as dened

in Table 3) and the parameter type. The setup, hold,

and propagation delay parameters, dened below, are

designated in the symbol name by the SET, HLD, and

DEL characters, respectively.

The values given for the parameters are the same as

those used during production testing and speed bin-

ning of the devices. The junction temperature and sup-

ply voltage used to characterize the devices are listed

in the delay tables. Actual delays at nominal tempera-

ture and voltage for best-case processes can be much

better than the values given.

It should be noted that the junction temperature used in

the tables is generally 85 °C. The junction temperature

for the FPGA depends on the power dissipated by the

device, the package thermal characteristics (

ΘJA), and

the ambient temperature, as calculated in the following

equation and as discussed further in the Package

Thermal Characteristics section:

TJmax = TAmax + (P

ΘJA) °C

Note

: The user must determine this junction tempera-

ture to see if the delays from ispLEVER should

be derated based on the following derating

tables.

ply and junction temperature derating for OR3Cxx com-

mercial and industrial devices. Table 40 provides the

same information for the OR3Txxx devices (both com-

mercial and industrial). The delay values in this data

sheet and reported by ispLEVER are shown as 1.00 in

the tables. The method for determining the maximum

junction temperature is dened in the Package Thermal

Characteristics section. Taken cumulatively, the range

of parameter values for best-case vs. worst-case pro-

cessing, supply voltage, and junction temperature can

approach 3 to 1.

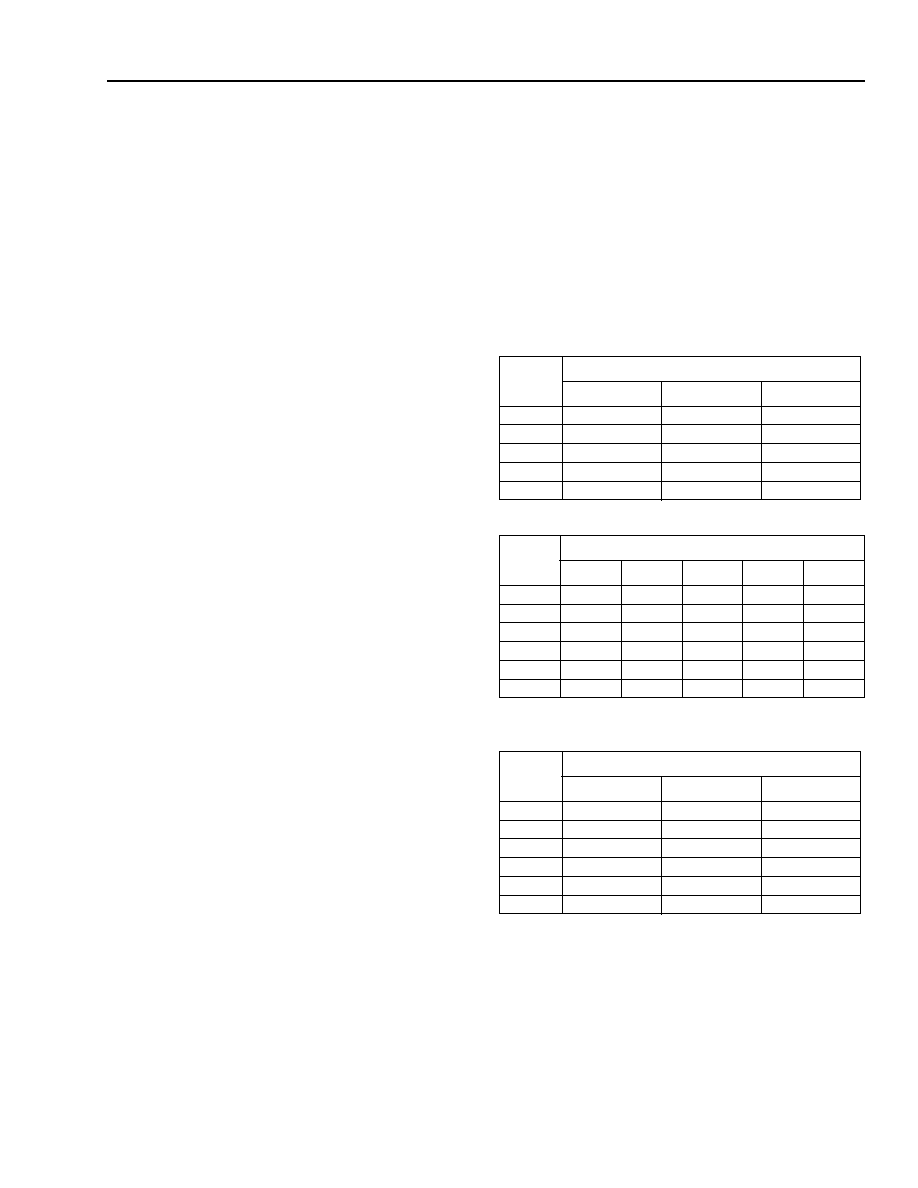

Table 38. Derating for Commercial Devices

(OR3Cxx)

Table 39. Derating for Industrial Devices (OR3Cxx)

Table 40. Derating for Commercial/Industrial

Devices (OR3Txxx)

Note: The derating tables shown above are for a typical critical path

that contains 33% logic delay and 66% routing delay. Since the

routing delay derates at a higher rate than the logic delay, paths

with more than 66% routing delay will derate at a higher rate

than shown in the table. The approximate derating values vs.

temperature are 0.26% per °C for logic delay and 0.45% per °C

for routing delay. The approximate derating values vs. voltage

are 0.13% per mV for both logic and routing delays at 25 °C.

TJ

(C)

Power Supply Voltage

4.75 V

5.0 V

5.25 V

0

0.81

0.79

0.77

25

0.85

0.83

0.81

85

1.00

0.97

0.95

100

1.05

1.02

1.00

125

1.12

1.09

1.07

TJ

(C)

Power Supply Voltage

4.5 V

4.75 V

5.0 V

5.25 V

5.5 V

—40

0.71

0.70

0.68

0.66

0.65

0

0.80

0.78

0.76

0.74

0.73

25

0.84

0.82

0.80

0.78

0.77

85

1.00

0.97

0.94

0.93

0.91

100

1.05

1.01

0.99

0.97

0.95

125

1.12

1.09

1.06

1.04

1.02

TJ

(C)

Power Supply Voltage

3.0 V

3.3 V

3.6 V

—40

0.73

0.66

0.61

0

0.82

0.73

0.68

25

0.87

0.78

0.72

85

1.00

0.90

0.83

100

1.04

0.94

0.87

125

1.10

1.00

0.92

Select

devices

have

been

discontinued.

See

Ordering

Information

section

for

product

status.

相关PDF资料 |

PDF描述 |

|---|---|

| OR3T307S240-DB | FPGA, 196 CLBS, 48000 GATES, PQFP240 |

| OR3T556PS240-DB | FPGA, 324 CLBS, 80000 GATES, PQFP240 |

| OR3T806PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T807PS240-DB | FPGA, 484 CLBS, 116000 GATES, PQFP240 |

| OR3T55-4BA256I | FPGA, 324 CLBS, 40000 GATES, 80 MHz, PBGA256 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR3T30-7BA256 | 制造商:AGERE 制造商全称:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T307BA256-DB | 功能描述:FPGA - 现场可编程门阵列 1568 LUT 221 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR3T30-7BA256I | 制造商:AGERE 制造商全称:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T30-7BA352 | 制造商:AGERE 制造商全称:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T30-7BA352I | 制造商:AGERE 制造商全称:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

发布紧急采购,3分钟左右您将得到回复。