- 您现在的位置:买卖IC网 > PDF目录69043 > PGA117AIPW (TEXAS INSTRUMENTS INC) SPECIALTY ANALOG CIRCUIT, PDSO20 PDF资料下载

参数资料

| 型号: | PGA117AIPW |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 模拟信号调理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| 封装: | GREEN, PLASTIC, TSSOP-20 |

| 文件页数: | 25/47页 |

| 文件大小: | 1545K |

| 代理商: | PGA117AIPW |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页

OP AMP: FREQUENCY RESPONSE VERSUS

ANALOG MUX

SR(V/ s)=2 f

V

(1

10 )

m

p

OP

-6

(4)

Example:

,, PGA113

www.ti.com ............................................................................................................................................ SBOS424B – MARCH 2008 – REVISED SEPTEMBER 2008

GAIN

The analog input MUX provides two input channels

Table 8 documents how small-signal bandwidth and

for the PGA112/PGA113 and 10 input channels for

slew rate change correspond to changes in PGA

the

PGA116/PGA117.

The

MUX

switches

are

gain.

designed to be break-before-make and thereby

eliminate any concerns about shorting the two input

Full power bandwidth (that is, the highest frequency

signal sources together.

that a sine wave can pass through the PGA for a

given gain) is related to slew rate by Equation 4:

Four internal MUX CAL channels are included in the

analog MUX for ease of system calibration. These

CAL channels allow ADC gain and offset errors to be

calibrated out. This calibration does not remove the

Where:

offset and gain errors of the PGA for gains greater

SR = Slew rate in V/

s

than 1, but most systems should see a significant

f = Frequency in Hz

increase in the ADC accuracy. In addition, these CAL

VOP = Output peak voltage in volts

channels can be used by the ADC to read the

minimum and maximum possible voltages from the

PGA. With these minimum and maximum levels

known, the system architecture can be designed to

For G = 8, then SR = 10.6V/

s (slew rate rise is

indicate an out-of-range condition on the measured

minimum slew rate).

analog

input

signals

if

these

levels

are

ever

For a 5V system, choose 0.1V < VOUT < 4.9V or

measured.

VOUTPP = 4.8V or VOUTP = 2.4V.

To use the CAL channels, VCAL/CH0 must be

SR (V/

s) = 2πf × V

OP (1 × 10

–6).

permanently connected to the system ADC reference.

10.6 = 2

πf (2.4) (1 × 10–6) → f = 702.9kHz

There is a typical 100k

load from VCAL/CH0 to

This example shows that a G = 8 configuration

ground. Table 9 illustrates how to use the CAL

can produce a 4.8VPP sine wave with frequency

up to 702.9kHz. This computation only shows the

to use the CAL channels with VREF = AVDD/2. The

theoretical upper limit of frequency for this

VREF pin must be connected to a source that is

example, but does not indicate the distortion of

low-impedance for both dc and ac in order to

the sine wave. The acceptable distortion depends

maintain gain and nonlinearity accuracy. Worst-case

on

the

specific

application.

As

a

general

current demand on the VREF pin occurs when G = 1

guideline,

maintain

two

to

three

times

the

because there is a 3.25k

resistor between VOUT and

calculated slew rate to minimize distortion on the

VREF. For a 5V system with AVDD/2 = 2.5V, the VREF

sine wave. For this example, the application

pin buffer must source and sink 2.5V/3.25k

= 0.7mA

should only use G = 8, 4.8VPP, up to a frequency

minimum for a VOUT that can swing from ground to

range of 234kHz to 351kHz, depending upon the

+5V.

acceptable distortion. For a given gain and slew

rate requirement, check for adequate small-signal

bandwidth (typical –3dB frequency) in order to

assure that the frequency of the signal can be

passed without attenuation.

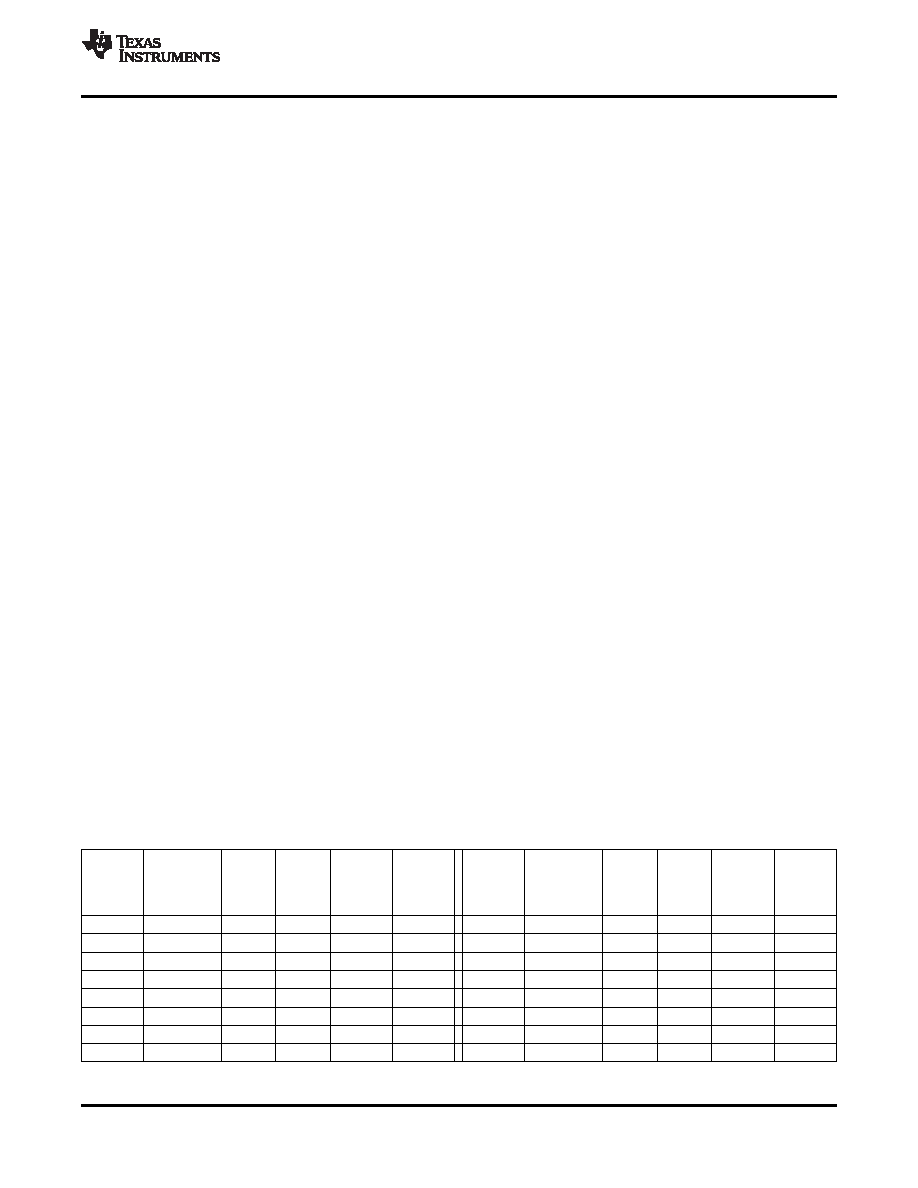

Table 8. Frequency Response versus Gain (CL = 100pF, RL= 10k)

0.1%

0.01%

0.1%

0.01%

TYPICAL

SLEW

SETTLING

TYPICAL

SLEW

SETTLING

–3dB

RATE-

TIME:

SCOPE

–3dB

RATE-

TIME:

BINARY

FREQUENCY

FALL

RISE

4VPP

GAIN

FREQUENCY

FALL

RISE

4VPP

GAIN (V/V)

(MHz)

(V/

s)

(V/

s)

(

s)

(

s)

(V/V)

(MHz)

(V/

s)

(V/

s)

(

s)

(

s)

1

10

8

3

2

2.55

1

10

8

3

2

2.55

2

3.8

9

6.4

2

2.6

2

3.8

9

6.4

2

2.6

4

2

12.8

10.6

2

2.6

5

1.8

12.8

10.6

2

2.6

8

1.8

12.8

10.6

2

2.6

10

1.8

12.8

10.6

2.2

2.6

16

1.6

12.8

2.3

2.6

20

1.3

12.8

9.1

2.3

2.8

32

1.8

12.8

13.3

2.3

3

50

0.9

9.1

7.1

2.4

3.8

64

0.6

4

3.5

3

6

100

0.38

4

3.5

4.4

7

128

0.35

2.5

4.8

8

200

0.23

2.3

2

6.9

10

Copyright 2008, Texas Instruments Incorporated

31

相关PDF资料 |

PDF描述 |

|---|---|

| PGA113AIDGSTG4 | SPECIALTY ANALOG CIRCUIT, PDSO10 |

| PGA113AIDGST | SPECIALTY ANALOG CIRCUIT, PDSO10 |

| PGA113AIDGSR | SPECIALTY ANALOG CIRCUIT, PDSO10 |

| PGA116AIPWG4 | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| PGA117AIPWRG4 | SPECIALTY ANALOG CIRCUIT, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PGA117AIPWG4 | 功能描述:特殊用途放大器 Programmable Gain Amp w/Mux RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel |

| PGA117AIPWR | 功能描述:特殊用途放大器 Zero-Drift Program Gain AMP/MUX RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel |

| PGA117AIPWRG4 | 功能描述:特殊用途放大器 Programmable Gain Amp w/Mux RoHS:否 制造商:Texas Instruments 通道数量:Single 共模抑制比(最小值): 输入补偿电压: 工作电源电压:3 V to 5.5 V 电源电流:5 mA 最大功率耗散: 最大工作温度:+ 70 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:QFN-20 封装:Reel |

| PGA-120-AH3-S-TG | 制造商:3M Electronic Products Division 功能描述: |

| PGA120M004B1-1315BLU | 制造商:FCI 功能描述: |

发布紧急采购,3分钟左右您将得到回复。