- 您现在的位置:买卖IC网 > PDF目录269903 > QL5810-66CPTN196I (QUICKLOGIC CORP) PCI BUS CONTROLLER, PBGA196 PDF资料下载

参数资料

| 型号: | QL5810-66CPTN196I |

| 厂商: | QUICKLOGIC CORP |

| 元件分类: | 总线控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA196 |

| 封装: | 12 X 12 MM, 1.20 MM HEIGHT, 0.80 MM PITCH, LEAD FREE, PLASTIC, MO-216C, TFBGA-196 |

| 文件页数: | 7/80页 |

| 文件大小: | 1125K |

| 代理商: | QL5810-66CPTN196I |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

2006 QuickLogic Corporation

QL58x0 Enhanced QuickPCI Target Family Data Sheet Rev. L

15

I/O Cell Structure

The QL58x0 device family features a variety of distinct I/O pins to maximize performance, functionality, and

flexibility with bi-directional I/O pins and input-only pins. All input and I/O pins are 1.8 V, 2.5 V, and 3.3 V

tolerant and comply with the specific I/O standard selected. For single ended I/O standards, VCCIO specifies

the input tolerance and the output drive. For voltage referenced I/O standards (e.g SSTL), the voltage supplied

to the INREF pins in each bank specifies the input switch point. For example, the VCCIO pins must be tied to

a 3.3 V supply to provide 3.3 V compliance. The QL58x0 device family can also support the LVDS and

LVPECL I/O standards with the use of external resistors (see Table 12).

As designs become more complex and requirements more stringent, several application-specific I/O standards

have emerged for specific applications. I/O standards for processors, memories, and a variety of bus

applications have become commonplace and a requirement for many systems. In addition, I/O timing has

become a greater issue with specific requirements for setup, hold, clock to out, and switching times. The

QL58x0 device family has addressed these new system requirements and now includes a completely new I/O

cell which consists of programmable I/Os as well as a new cell structure consisting of three registers—Input,

Output, and OE.

The QL58x0 device family offers banks of programmable I/Os that address many of the bus standards that

are popular today. As shown in Figure 8 each bi-directional I/O pin is associated with an I/O cell which

features an input register, an input buffer, an output register, a three-state output buffer, an output enable

register, and 2 two-to-one output multiplexers.

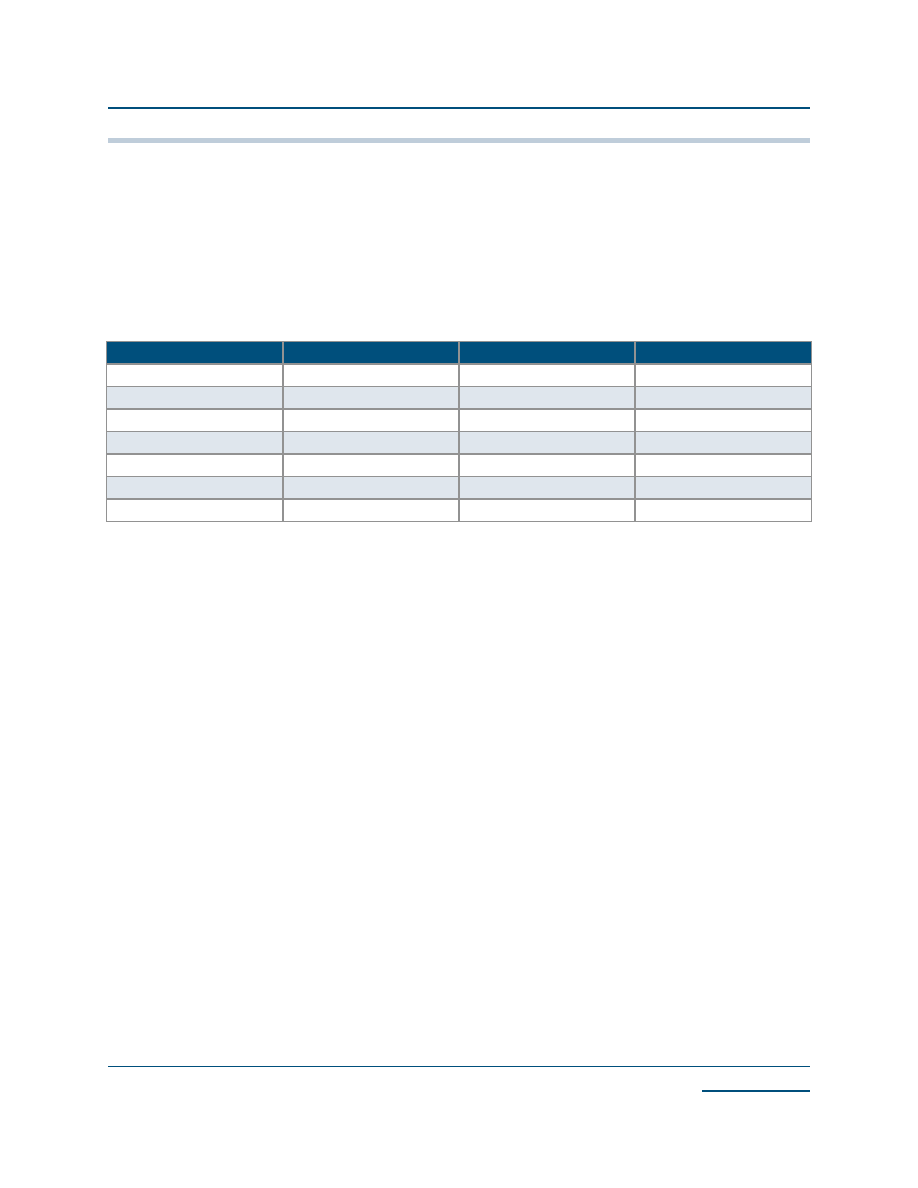

Table 12: I/O Standards and Applications

I/O Standard

Reference Voltage

Output Voltage

Application

LVTTL

n/a

3.3 V

General Purpose

LVCMOS25

n/a

2.5 V

General Purpose

LVCMOS18

n/a

1.8 V

General Purpose

PCI

n/a

3.3 V

PCI Bus Applications

GTL+

1

n/a

Backplane

SSTL3

1.5

3.3 V

SDRAM

SSTL2

1.25

2.5 V

SDRAM

相关PDF资料 |

PDF描述 |

|---|---|

| QL5820-33BPTN196C | PCI BUS CONTROLLER, PBGA196 |

| QL5842-33BPSN484M | PCI BUS CONTROLLER, PBGA484 |

| QT83C154XXX-L | 8-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP44 |

| QC87C251SQ | 8-BIT, UVPROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| QR80C51XXX:R | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| QL5822-33BPTN280C-5695 | 制造商:QuickLogic Corporation 功能描述: |

| QL62506PB516C | 制造商:QUICK LOG 功能描述:New |

| QL6325PQ208 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ASIC |

| QL6325PT280 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:ASIC |

| QL63D5SA | 制造商:未知厂家 制造商全称:未知厂家 功能描述:InGaAlP Laser Diode |

发布紧急采购,3分钟左右您将得到回复。