- 您现在的位置:买卖IC网 > PDF目录98143 > ST52E430B/D (STMICROELECTRONICS) 8-BIT, UVPROM, 20 MHz, MICROCONTROLLER, CDIP32 PDF资料下载

参数资料

| 型号: | ST52E430B/D |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, UVPROM, 20 MHz, MICROCONTROLLER, CDIP32 |

| 封装: | WINDOWED, SHRINK, CERAMIC, DIP-32 |

| 文件页数: | 42/120页 |

| 文件大小: | 502K |

| 代理商: | ST52E430B/D |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页

28/120

ST52T430/E430

INT_ADC

INT_TIMER/PWM2

INT_SCI

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

INTERRUPT

VECTORS

INT_EXT

18

19

20

INT_TIMER/PWM1

INT_TIMER/PWM0

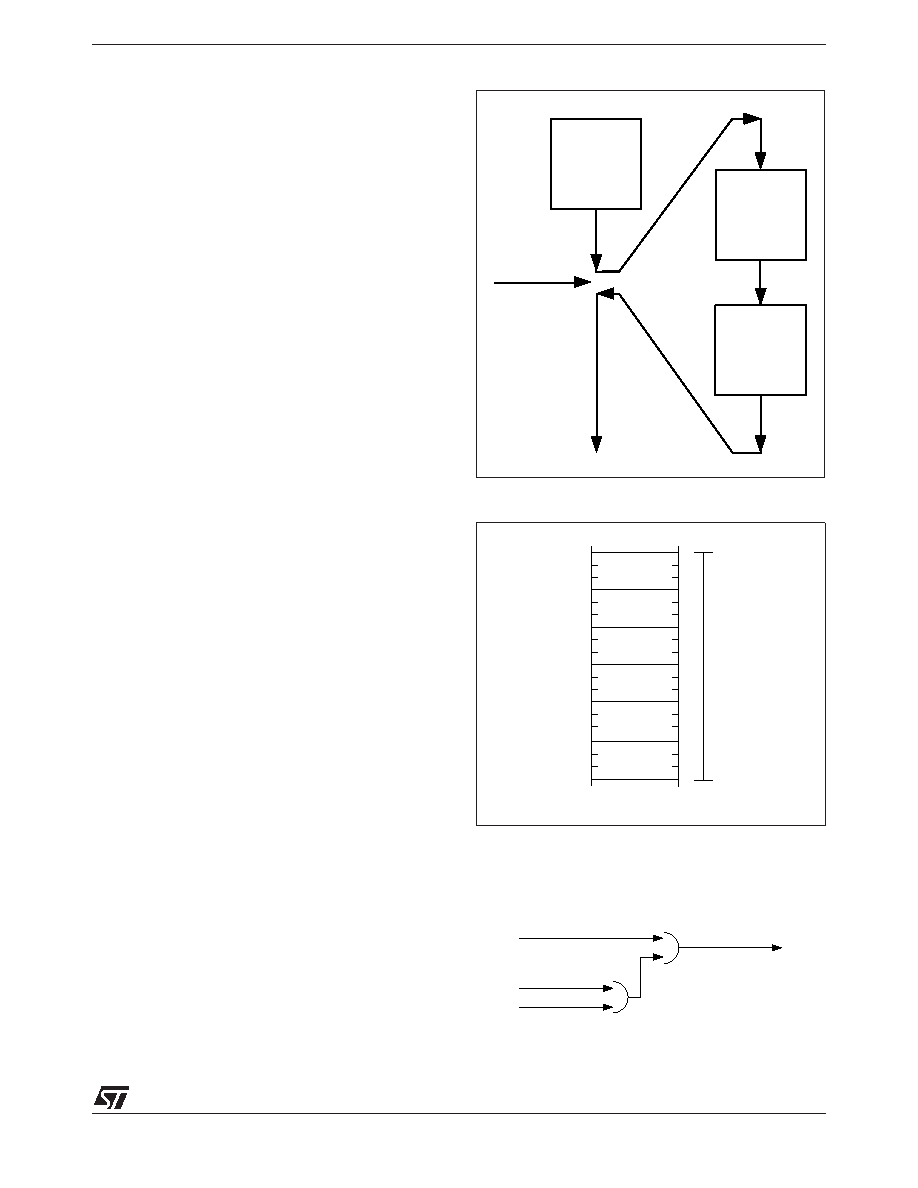

Figure 4.2. Interrupt Vectors Mapping

4 INTERRUPTS

The Control Unit (CU) responds to peripheral

events and external events through its interrupt

channels.

When such an event occurs, if the related interrupt

is not masked and according to a priority order, the

current program execution can be suspended to

allow the CU to execute a specific response

routine.

Each interrupt is associated with an interrupt

vector that contains the memory address of the

related interrupt service routine. Each vector is

located in the Program Space (EPROM Memory)

at a fixed address (see Interrupt Vectors table fig.

4.2).

4.1 Interrupt Functionment

If, at the end of an arithmetic or logic instruction,

there are pending interrupts, the one with the

highest priority is passed. To pass an interrupt

means to store the arithmetic flags and the current

PC in the stack and execute the associated

Interrupt routine, whose address is located in two

bytes of the EPROM memory location between

address 3 and 20.

The Interrupt routine is performed as a normal

code checking, at the end of each instruction, if an

higher priority interrupt has to be passed. An

Interrupt request with the higher priority stops the

lower priority Interrupt. The Program Counter and

the arithmetic flags are stored in the stack.

With the instruction RETI (Return from Interrupt)

the arithmetic flags and Program Counter (PC) are

restored from the top of the stack. This stack was

already described in the section 2.2.1.

An Interrupt request cannot stop the processing of

the fuzzy rules, but this is passed only after the end

of a fuzzy rule or at the end of a logic, or arithmetic,

instruction.

4.2 Global Interrupt Request Enabling

When an Interrupt occurs, it generates a Global

Interrupt Pending (GIP), that can be hanged up by

software. After a GIP a Global Interrupt Request

(GIR) will be generated and Interrupt Service

Routine associated to the interrupt with higher

priority will start.

In order to avoid possible conflicts between

interrupt masking set in the main program, or

inside macros, the GIP is hanged up through the

User Global Interrupt Mask or the Macro Global

Interrupt Mask (see fig.4.3).

UEGI/UDGI instruction switches on/off the User

Global Interrupt Mask enabling/disabling the GIR

for the main program.

NORMAL

PROGRAM

FLOW

INTERRUPT

SERVICE

ROUTINE

RETI

INSTRUCTION

INTERRUPT

Figure 4.1. Interrupt Flow

Global Interrupt

Pending

User Global

Interrupt Mask

Macro Global

Interrupt Mask

Global Interrupt

Request

Figure 4.3 Global Interrupt Request generation

相关PDF资料 |

PDF描述 |

|---|---|

| ST52F510F1M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO20 |

| ST52F510G0B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 |

| ST52F513F0M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO20 |

| ST52F513F1B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP20 |

| ST52F513G1M6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST52E430K1B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K1M6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K1T6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K2B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

| ST52E430K2M6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Three Timer/PWMs, ADC, SCI |

发布紧急采购,3分钟左右您将得到回复。