- 您现在的位置:买卖IC网 > PDF目录69378 > ST7PLITEUS5M6TR (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO8 PDF资料下载

参数资料

| 型号: | ST7PLITEUS5M6TR |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO8 |

| 封装: | 0.150 INCH, LEAD FREE, PLASTIC, SOP-8 |

| 文件页数: | 59/108页 |

| 文件大小: | 1957K |

| 代理商: | ST7PLITEUS5M6TR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页

ST7LITEUSx

54/108

12-BIT AUTORELOAD TIMER (Cont’d)

10.2.6 Register Description

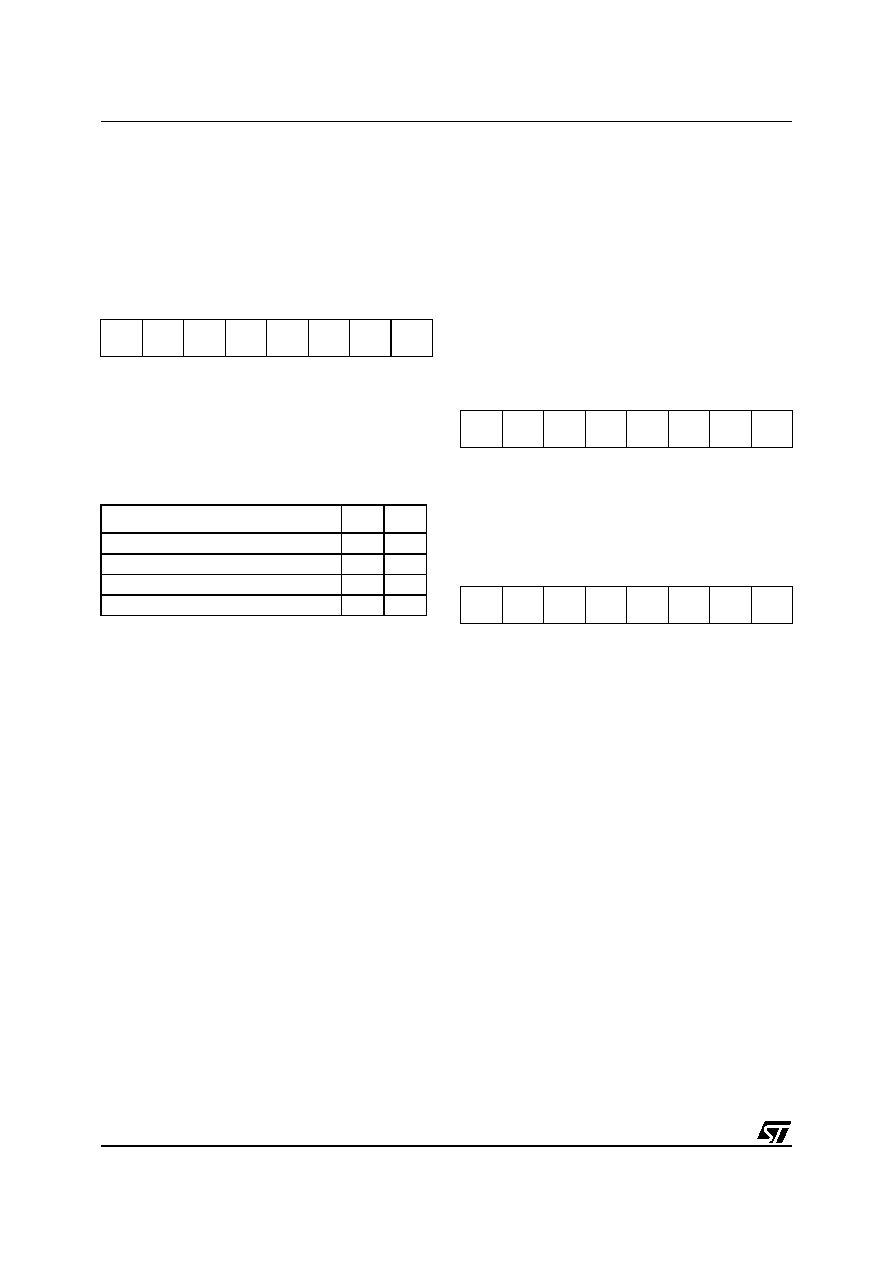

TIMER CONTROL STATUS REGISTER (ATC-

SR)

Read / Write

Reset Value: 0000 0000 (00h)

Bits 7:5 = Reserved, must be kept cleared.

Bits 4:3 = CK[1:0] Counter Clock Selection.

These bits are set and cleared by software and

cleared by hardware after a reset. They select the

clock frequency of the counter.

Bit 2 = OVF Overflow Flag.

This bit is set by hardware and cleared by software

by reading the ATCSR register. It indicates the

transition of the counter from FFFh to ATR value.

0: No counter overflow occurred

1: Counter overflow occurred

Caution:

When set, the OVF bit stays high for 1 fCOUNTER

cycle (up to 1ms depending on the clock selection)

after it has been cleared by software.

Bit 1 = OVFIE Overflow Interrupt Enable.

This bit is read/write by software and cleared by

hardware after a reset.

0: OVF interrupt disabled

1: OVF interrupt enabled

Bit 0 = CMPIE Compare Interrupt Enable.

This bit is read/write by software and clear by

hardware after a reset. It allows to mask the inter-

rupt generation when CMPF bit is set.

0: CMPF interrupt disabled

1: CMPF interrupt enabled

COUNTER REGISTER HIGH (CNTRH)

Read only

Reset Value: 0000 0000 (00h)

COUNTER REGISTER LOW (CNTRL)

Read only

Reset Value: 0000 0000 (00h)

Bits 15:12 = Reserved, must be kept cleared.

Bits 11:0 = CNTR[11:0] Counter Value.

This 12-bit register is read by software and cleared

by hardware after a reset. The counter is incre-

mented continuously as soon as a counter clock is

selected. To obtain the 12-bit value, software

should read the counter value in two consecutive

read operations. As there is no latch, it is recom-

mended to read LSB first. In this case, CNTRH

can be incremented between the two read opera-

tions and to have an accurate result when

ftimer=fCPU, special care must be taken when CN-

TRL values close to FFh are read.

When a counter overflow occurs, the counter re-

starts from the value specified in the ATR register.

70

0

CK1

CK0

OVF

OVFIE CMPIE

Counter Clock Selection

CK1

CK0

OFF

0

fLTIMER (1 ms timebase @ 8 MHz)

0

1

fCPU

10

Reserved

1

15

8

0

CN11

CN10

CN9

CN8

70

CN7

CN6

CN5

CN4

CN3

CN2

CN1

CN0

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST7PLITEUS5M6 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO8 |

| ST7FLITEUS5M3TR | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO8 |

| ST7FLITEUS2B3 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP8 |

| ST7FSCR1E4U1 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, QCC64 |

| ST7SCR1T1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7PLITEUS5U3 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit MCU with single voltage Flash memory, ADC, timers |

| ST7PLITEUS5U3TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit MCU with single voltage Flash memory, ADC, timers |

| ST7PLITEUS5U6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit MCU with single voltage Flash memory, ADC, timers |

| ST7PLITEUS5U6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit MCU with single voltage Flash memory, ADC, timers |

| ST7PMC1K2B3 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-bit MCU with nested interrupts, Flash, 10-bit ADC, brushless motor control, five timers, SPI, LINSCI? |

发布紧急采购,3分钟左右您将得到回复。