- 您现在的位置:买卖IC网 > PDF目录98158 > TAS3218IPZPR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TAS3218IPZPR |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | GREEN, PLASTIC, TQFP-100 |

| 文件页数: | 61/79页 |

| 文件大小: | 1263K |

| 代理商: | TAS3218IPZPR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页当前第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

Load Memory Control and Data Register (0x04 and 0x05)

SLES235 – JULY 2008 ....................................................................................................................................................................................................... www.ti.com

Bits 4032 define the memory load error status on EEPROM download and slave download.

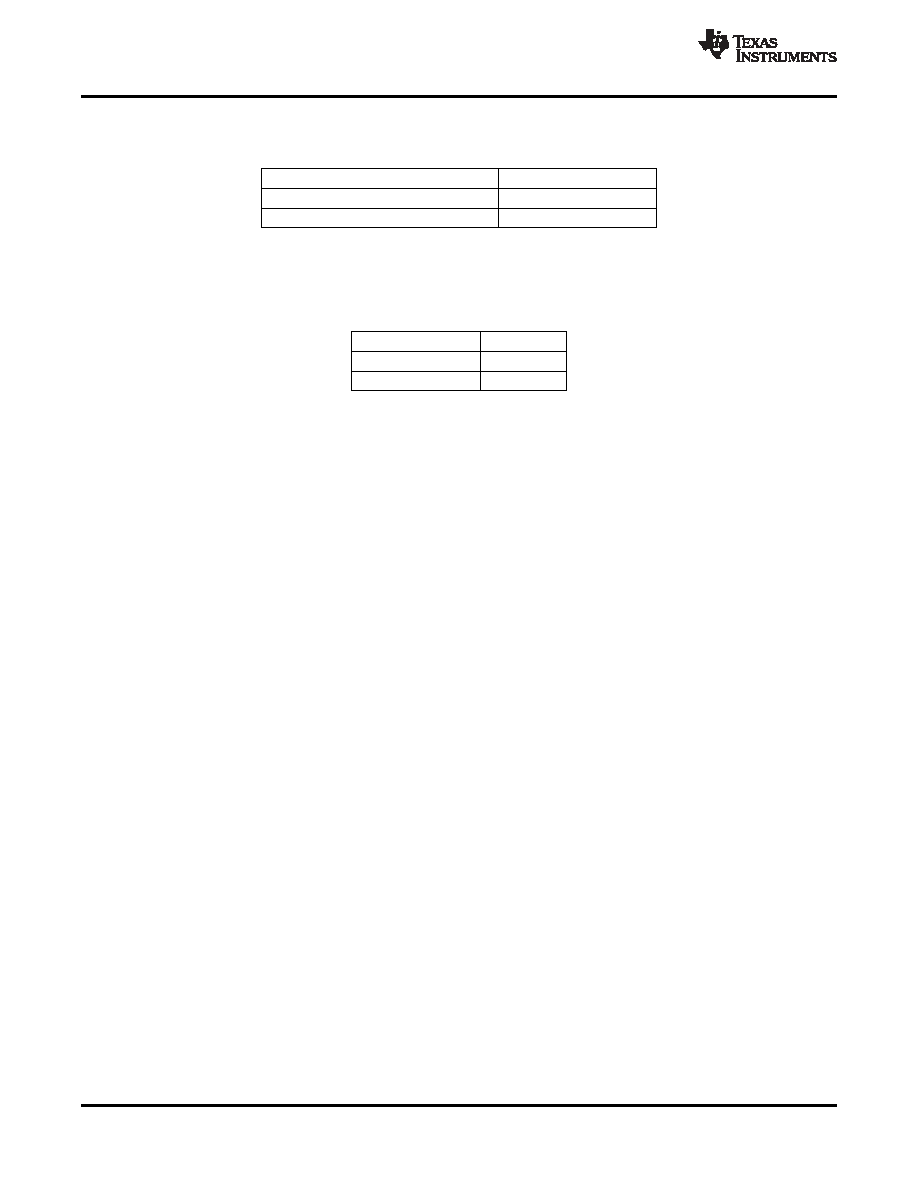

Table 26. Analog Busy(1)

ANALOG BUSY FLAG

ABSY

Analog is busy

1

Analog not busy

0

(1)

Default values are shown in italics.

Analog control sequence takes time (maximum around 500 ms for headphone power up). This busy flag indicate

whether analog control sequence is running or not.

Table 27. I2C Bus Error(1)

I2C BUS ERROR

BUSE

Bus error

1

No bus error

0

(1)

Default values are shown in italics.

If I2C bus error occurs, this flag will be set. Only host uC can clear this flag by writing 0 to this bit. I2C bus error

status is read from ESFR (0xC5, bit 6), and is cleared by ESFR (0xC7, bit 6).

The I2C Memory Load port permits the system controller to load the TAS3218 memories as an alternative to

having the TAS3218 load its memory from an external EEPROM.

The transfer is performed by writing to two I2C registers. The first register is a eight byte register than holds the

check sum, the memory to be written, the starting address, the number of data bytes to be transferred. The

second register holds eight bytes of data.

The memory load operation starts with the first register being set. Then the data is written into the second

register using the format shown. After the last data byte is written into the second register, an additional two

bytes are written which constrain the two byte checksum. At that point, the transfer is complete and status of the

operation is reported in the status register.

NOTE:

Once the micro program memory has been loaded, further updates to this memory

are inhibited until the device is RESET.

When the first I2C slave down load register is written by the system controller the TAS3218 will update the status

register by setting a error bit to indicate an error for the memory type that is being loaded. This error bit is reset

when the operation complete and a valid checksum has been received.

For example when the Micro program memory is being loaded, the TAS3218 will set a Micro program memory

error indication in the status register at the start of the sequence. When the last byte of the micro program

memory and checksum is received, the TAS3218 will clear the micro program memory error indication. This

enables the TAS3218 to preserve any error status indications that occur as a result of incomplete transfers of

data/ checksum error during a series of data and program memory load operations.

The checksum is always contained in the last two bytes of the data block.

The I2C slave download is terminated when a termination header with a zero length byte count filed is received.

64

Copyright 2008, Texas Instruments Incorporated

Product Folder Link(s): TAS3218

相关PDF资料 |

PDF描述 |

|---|---|

| TAS3218IPZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218PZPR | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS5000PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TAS5000PFBG4 | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TAS3218PZP | 功能描述:音频 DSP Dig Audio SoC for multi-channel app RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS3218PZPR | 功能描述:音频 DSP Dig Audio SoC for multi-channel app RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS-3225A | 制造商:TEW 功能描述: |

| TAS-3225A 44.000KHZ | 制造商:TEW 功能描述: |

| TAS-3225J 13.56MHz }20ppm/22pF | 制造商:Tokyo Denpa 功能描述:13.560000MHz }20ppm }15ppm 22pF 3.2~2.5~0.55mm +85 -30 3.2mm 2.5mm 0.55mm Cut Tape |

发布紧急采购,3分钟左右您将得到回复。