- 您现在的位置:买卖IC网 > PDF目录19457 > TMS320VC5409PGE-80 (Texas Instruments)IC FIXED POINT DSP 144-LQFP PDF资料下载

参数资料

| 型号: | TMS320VC5409PGE-80 |

| 厂商: | Texas Instruments |

| 文件页数: | 29/93页 |

| 文件大小: | 0K |

| 描述: | IC FIXED POINT DSP 144-LQFP |

| 标准包装: | 60 |

| 系列: | TMS320C54x |

| 类型: | 定点 |

| 接口: | 主机接口,McBSP |

| 时钟速率: | 80MHz |

| 非易失内存: | ROM(32 kB) |

| 芯片上RAM: | 64kB |

| 电压 - 输入/输出: | 3.30V |

| 电压 - 核心: | 1.80V |

| 工作温度: | -40°C ~ 100°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 144-LQFP |

| 供应商设备封装: | 144-LQFP(20x20) |

| 包装: | 托盘 |

| 配用: | 296-15829-ND - DSP STARTER KIT FOR TMS320C5416 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页

Functional Overview

35

April 1999 Revised October 2008

SPRS082F

3.3.2.1

Sample Rate Generator

The 5409 sample rate generator has four clock input options that are only available when both the PCR and

SRGR2 are used. Table 38 shows the sample rate generator clock input options.

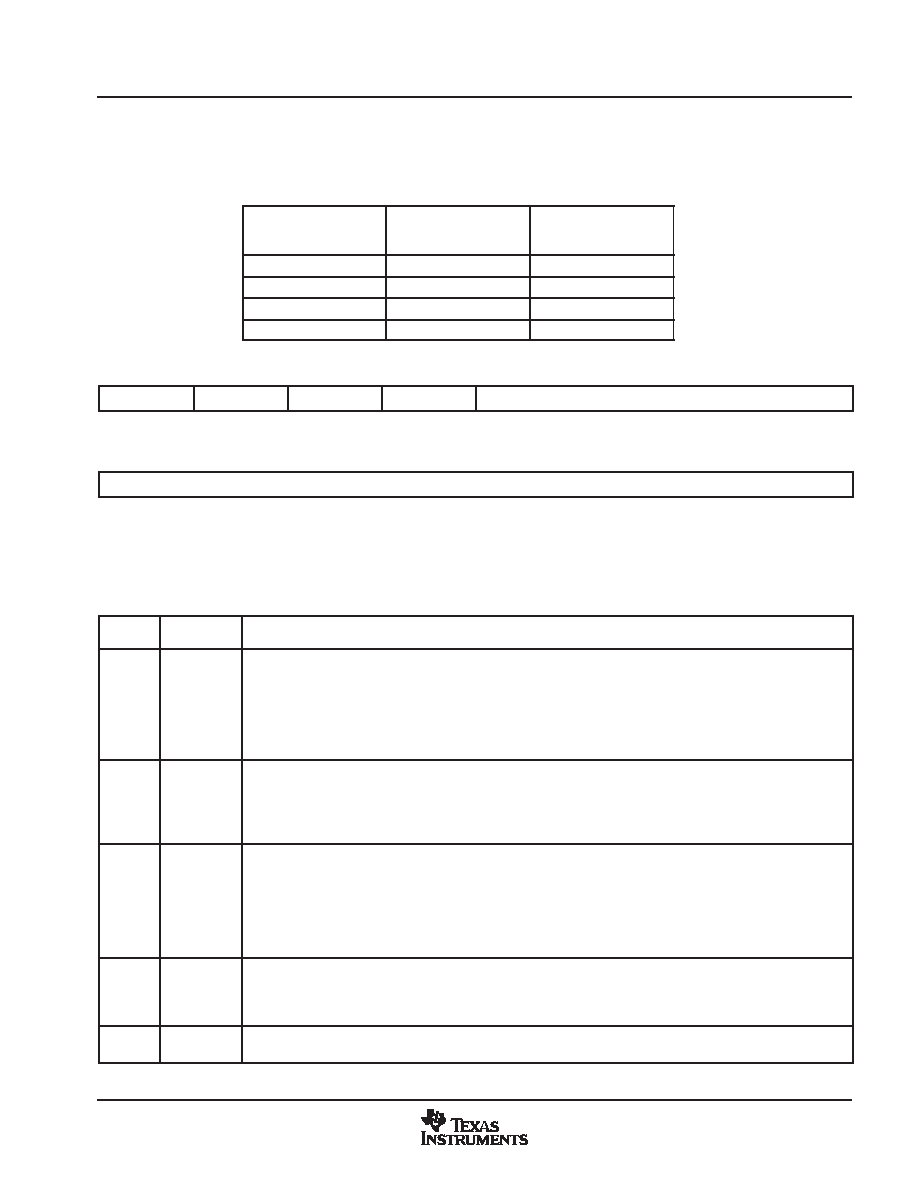

Table 38. Sample Rate Generator Clock Input Options

MODE

SCLKME

(PCR.7)

CLKSM

(SRGR2.13)

CLKS pin

0

CPU

0

1

CLKR pin

1

0

CLKX pin

1

15

14

13

12

11

8

GSYNC

CLKSP

CLKSM

FSGM

FPER

R/W-0

R/W

7

0

FPER

R/W

LEGEND: R = Read, W = Write, n = value present after reset

Figure 39. Sample Rate Generator Register 2 (SRGR2)

Table 39. Sample Rate Generator Register 2 (SRGR2) Bit Field Descriptions

BIT

NAME

FUNCTION

BIT

NAME

FUNCTION

15

GSYNC

Sample rate generator clock synchronization. Only used when the external clock (CLKS) drives the sample rate

generator clock (CLKSM=0)

GSYNC = 0

The sample rate generator clock (CLKG) is free-running.

GSYNC = 1

The sample rate generator clock (CLKG) is running. But CLKG is resynchronized and frame sync

signal (FSG) is generated only after detecting the receive frame synchronization signal (FSR). Also,

frame period (FPER) is a don’t care because the period is dictated by the external frame sync pulse.

14

CLKSP

CLKS polarity clock edge select. Only used when the external clock (CLKS) drives the sample rate generator clock

(CLKSM=0).

CLKSP = 0

Rising edge of CLKS generates CLKG and FSG.

CLKSP = 1

Falling edge of CLKS generates CLKG and FSG.

13

CLKSM

McBSP sample rate generator clock mode

SCLKME = 0

CLKSM = 0

Sample rate generator clock derived from the CLKS pin

(in PCR)

CLKSM = 1

Sample rate generator clock derived from CPU clock

SCLKME = 1

CLKSM = 0

Sample rate generator clock derived from CLKR pin

(in PCR)

CLKSM = 1

Sample rate generator clock derived from CLKX pin

12

FSGM

Sample rate generator transmit frame synchronization mode. Used when FSXM=1 in the PCR.

FSGM = 0

Transmit frame sync signal (FSX) due to DXR(1/2) copy

FSGN = 1

Transmit frame sync signal driven by the sample rate generator frame sync signal (FSG)

11 0

FPER

Frame period. This determines when the next frame sycn signal should become active. Range: up to 212;

1 to 4096 CLKG periods.

相关PDF资料 |

PDF描述 |

|---|---|

| RSA06DTKH | CONN EDGECARD 12POS DIP .125 SLD |

| VJ1206Y681KBEAT4X | CAP CER 680PF 500V 10% X7R 1206 |

| 172-015-102R011 | CONN DB15 MALE SOLDER CUP TIN |

| BWR-15/670-D12A-C | CONV DC/DC +/-15V +/-670MA DIP |

| VJ1206Y682KBAAT4X | CAP CER 6800PF 50V 10% X7R 1206 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TMS320VC5409ZGU100 | 功能描述:数字信号处理器和控制器 - DSP, DSC Fixed-Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320VC5409ZGU-80 | 功能描述:数字信号处理器和控制器 - DSP, DSC Fixed-Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320VC5410AGGU1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TMS320VC5410AGGU12 | 功能描述:数字信号处理器和控制器 - DSP, DSC Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| TMS320VC5410AGGU16 | 功能描述:数字信号处理器和控制器 - DSP, DSC Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。