- 您现在的位置:买卖IC网 > PDF目录16138 > TS-MAC-E2-U4 (Lattice Semiconductor Corporation)IP CORE ETH MAC TRI-SPEED EC/ECP PDF资料下载

参数资料

| 型号: | TS-MAC-E2-U4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 17/66页 |

| 文件大小: | 0K |

| 描述: | IP CORE ETH MAC TRI-SPEED EC/ECP |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | TSMACE2U4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

�� �

�

Lattice� Semiconductor�

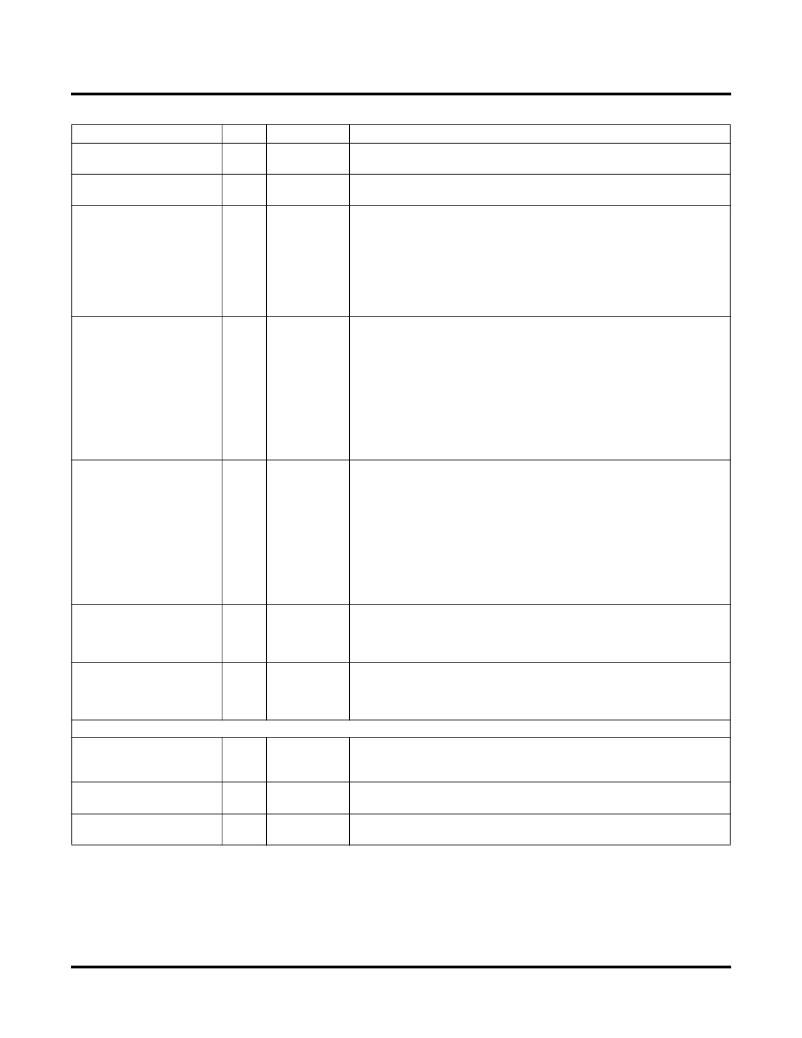

�Table� 2-1.� TSMAC� IP� Core� Input� and� Output� Signals�

�Functional� Description�

�txen�

�txer�

�Port� Name�

�Type�

�Output�

�Output�

�Active� State�

�High�

�High�

�Description�

�Transmit� Enable� .� Asserted� by� the� TSMAC� IP� core� to� indicate� the� txd�

�bus� contains� valid� frame.�

�Transmit� Error� .� Asserted� when� the� TSMAC� IP� core� generates� a� coding�

�error� on� the� byte� currently� being� transferred.�

�Receive� Data� Valid� .� Indicates� the� data� on� the� rxd� bus� is� valid.� Rxdv� is�

�used� in� the� SGMII� Easy� Connect� MAC� option� and� the� Gigabit� MAC�

�rxdv_pos� 1�

�rxdv_neg� 1�

�rxdv� 2�

�Input�

�High�

�option.� Rxdv_pos� and� rxdv_neg� are� used� only� in� the� Classic� TSMAC� IP�

�core� interface� option.� This� signal� is� pipelined� before� entering� the� core�

�with� the� rx_clk.� Note� the� “_pos”� signals� are� sampled� on� the� rising� edge�

�of� the� rxmac_clk� and� the� “_neg”� signals� are� sampled� on� the� falling� edge�

�of� the� rxmac_clk,� before� being� presented� to� the� MAC� core.�

�See� Figure� 2-6� .�

�Receive� Data� Bus� .� Data� is� driven� by� the� PHY� on� these� lines,� and� is�

�valid� whenever� rxdv� is� asserted.� These� signals� are� pipelined� before�

�entering� the� core� with� the� rxmac_clk.� Note� the� “_pos”� signals� are� sam-�

�rxd_pos[7:0]� 1�

�rxd_neg[3:0]� 1�

�rxd[7:0]� 2�

�Input�

�N/A�

�pled� on� the� rising� edge� of� the� rxmac_clk� and� the� “_neg”� signals� are� sam-�

�pled� on� the� falling� edge� of� the� rxmac_clk,� before� being� presented� to� the�

�MAC� core.� See� Figure� 2-6� .�

�rxd[7:0]� -� Receive� Data� from� the� PHY� Interface� .� These� GMII� Rx� data�

�inputs� (valid� whenever� rxdv� is� asserted)� come� from� the� SGMII_PCS� IP�

�core� (SGMII� Easy� Connect� option)� or� from� the� 1G� GMII� PHY� interface�

��Receive� Data� Error� .� This� signal� is� asserted� by� the� external� PHY� device�

�when� it� detects� an� error� during� frame� reception.� This� signal� is� pipelined�

�before� entering� the� core� with� the� rxmac_clk.� Note� the� “_pos”� signals� are�

�rxer_pos� 1�

�rxer_neg� 1�

�rxer� 2�

�Input�

�High�

�sampled� on� the� rising� edge� of� the� rxmac_clk� and� the� “_neg”� signals� are�

�sampled� on� the� falling� edge� of� the� rxmac_clk,� before� being� presented� to�

�the� MAC� core.� See� Figure� 2-6� .�

�rxer� -� Receive� Data� Error� from� the� PHY� Interface� .� This� GMII� Rx� error�

�input� comes� from� the� SGMII_PCS� IP� core� (SGMII� Easy� Connect� option)�

�or� from� the� 1G� GMII� PHY� interface� (Gigabit� MAC� option).� See� Figure� 2-7�

��Collision� .� This� active-high� signal� indicates� a� collision� occurred� during�

�col�

�Input�

�High�

�transmission.� This� signal� is� valid� for� half-duplex� operation� in� Fast� Ether-�

�net� (10/100)� for� the� Classic� and� SGMII� Easy� Connect� options� only.� Oth-�

�erwise,� it� is� ignored.�

�Carrier� Sense� .� This� signal,� when� logic� high,� indicates� the� network� has�

�crs�

�Input�

�High�

�activity.� Otherwise,� it� indicates� the� network� is� idle.� This� signal� is� valid� for�

�half-duplex� operation� in� Fast� Ethernet� (10/100)� for� the� Classic� and�

�SGMII� Easy� Connect� options� only.�

�Receive� MAC� Application� Interface�

�Receive� FIFO� Full� .� This� signal� indicates� the� Rx� FIFO� is� full� and� cannot�

�rx_fifo_full�

�Input�

�High�

�accept� any� more� data.� This� is� an� error� condition� and� should� never� hap-�

�pen.�

�rx_write�

�rx_dbout[7:0]�

�Output�

�Output�

�High�

�N/A�

�Receive� FIFO� Write� .� This� signal� is� asserted� by� the� TSMAC� IP� core� to�

�request� a� FIFO� write.�

�Receive� FIFO� Data� Output� .� This� bus� contains� the� data� that� is� to� be� writ-�

�ten� into� the� Receive� FIFO.�

�IPUG51_03.0,� December� 2010�

�17�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| IMC1210ER6R8K | INDUCTOR WW 6.8UH 10% 1210 |

| IMC1210ER5R6K | INDUCTOR WW 5.6UH 10% 1210 |

| IMC1210ER4R7K | INDUCTOR WW 4.7UH 10% 1210 |

| IMC1210ER3R9K | INDUCTOR WW 3.9UH 10% 1210 |

| IMC1210ER3R3K | INDUCTOR WW 3.3UH 10% 1210 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TS-MAC-E2-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-U3 | 功能描述:开发软件 Tri-Speed ethernet MAC RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-U4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TSMACP2U2 | 功能描述:以太网模块 TriSpd Ethernet MAC RoHS:否 制造商:Lantronix 产品:Device Servers 数据速率:300 bps to 921.6 kbps, 10 Mbps, 100 Mbps 接口类型:Ethernet, Serial 工作电源电压:5 V to 15 V 工作电源电流:133 mA to 400 mA 最大工作温度:+ 70 C |

发布紧急采购,3分钟左右您将得到回复。