- 您现在的位置:买卖IC网 > PDF目录16138 > TS-MAC-E2-U4 (Lattice Semiconductor Corporation)IP CORE ETH MAC TRI-SPEED EC/ECP PDF资料下载

参数资料

| 型号: | TS-MAC-E2-U4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 9/66页 |

| 文件大小: | 0K |

| 描述: | IP CORE ETH MAC TRI-SPEED EC/ECP |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | TSMACE2U4 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

�� �

�

Lattice� Semiconductor�

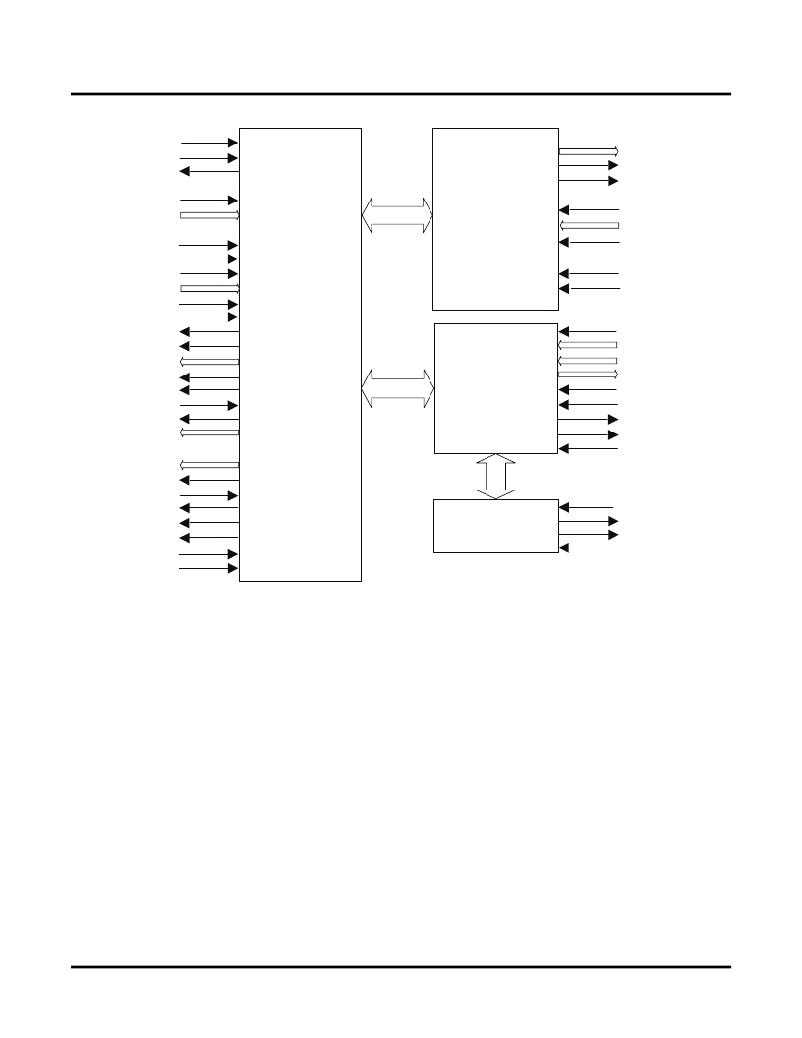

�Figure� 2-2.� Core� Block� Diagram� for� the� 1G� or� SGMII� Configurable� Options�

�rxmac_clk�

�txmac_clk�

�cpu_if_gbit_en�

�Functional� Description�

�txd�

�txen�

�txer�

�reset_n�

�tx_fifodata�

�tx_fifoavail�

�tx_fifoeof�

�tx_fifoempty�

�tx_sndpaustim�

�tx_sndpausreq�

�tx_fifoctrl�

�tx_staten�

�tx_macread�

�tx_statvec�

�tx_done�

�tx_disfrm�

�rx_fifo_full�

�rx_write�

�rx_dbout�

�Receive� and�

�Transmit� MAC�

�G/MII�

�Host�

�Interface�

�rxdv�

�rxd�

�rxer�

�col**�

�crs**�

�hcs_n�

�haddr�

�hdatain�

�hdataout�

�hwrite_n�

�hread_n�

�hready_n�

�hdataout_en_n�

�hclk�

�rx_stat_vector�

�rx_stat_en�

�ignore_next_pkt�

�rx_eof�

�mdc�

�rx_error�

�rx_fifo_error�

�rxmac_clk_en*�

�Management�

�Interface�

�mdo�

�mdio_en�

�mdi�

�txmac_clk_en*�

�*� These� inputs� are� only� present� for� the� SGMII� Easy� Connect� option.�

�**� These� inputs� are� not� present� for� the� Gigabit� MAC� option.�

�Functional� Overview�

�The� TSMAC� IP� core� transmits� and� receives� data� between� a� client� application� and� an� Ethernet� network.� The� main�

�function� of� the� Ethernet� MAC� is� to� ensure� that� the� Media� Access� rules� specified� in� the� 802.3� IEEE� standard� are� met�

�while� transmitting� and� receiving� Ethernet� frames.� Figure� 2-3� ,� Figure� 2-4� ,� and� Figure� 2-5� show� some� of� the� frame�

�formats� of� data� transmitted� and� received� on� the� Ethernet� network� that� the� TSMAC� IP� core� supports.�

�On� the� receiving� side,� the� Ethernet� MAC� extracts� the� different� components� of� a� frame� and� transfers� them� to� higher�

�applications� through� the� client� FIFO� interface.�

�The� data� received� from� the� G/MII� interface� is� first� buffered� until� sufficient� data� is� available� to� be� processed� by� the�

�Receive� MAC� (Rx� MAC).� The� Preamble� and� the� Start-of-Frame� Delimiter� (SFD)� information� are� then� extracted�

�from� the� incoming� frame� to� determine� the� start� of� a� valid� frame.� The� Receive� MAC� checks� the� address� of� the�

�received� packet� and� validates� whether� the� frame� can� be� received� before� transferring� it� into� the� FIFO.� Only� valid�

�frames� are� transferred� into� the� FIFO� (runts� and� fragments� are� discarded).� The� Rx� MAC� also� provides� a� statistics�

�vector� on� a� per� packet� basis� that� can� be� used� by� the� application.� The� TSMAC� IP� core� always� calculates� CRC� to�

�check� whether� the� frame� was� received� error-free.�

�On� the� transmit� side,� the� Tx� MAC� is� responsible� for� controlling� access� to� the� physical� medium.� The� Tx� MAC� reads�

�data� from� an� external� client� Tx� FIFO,� formats� this� data� into� an� Ethernet� packet� and� passes� it� to� the� G/MII� module.�

�IPUG51_03.0,� December� 2010�

�9�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| IMC1210ER6R8K | INDUCTOR WW 6.8UH 10% 1210 |

| IMC1210ER5R6K | INDUCTOR WW 5.6UH 10% 1210 |

| IMC1210ER4R7K | INDUCTOR WW 4.7UH 10% 1210 |

| IMC1210ER3R9K | INDUCTOR WW 3.9UH 10% 1210 |

| IMC1210ER3R3K | INDUCTOR WW 3.3UH 10% 1210 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TS-MAC-E2-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-U3 | 功能描述:开发软件 Tri-Speed ethernet MAC RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-U4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TSMACP2U2 | 功能描述:以太网模块 TriSpd Ethernet MAC RoHS:否 制造商:Lantronix 产品:Device Servers 数据速率:300 bps to 921.6 kbps, 10 Mbps, 100 Mbps 接口类型:Ethernet, Serial 工作电源电压:5 V to 15 V 工作电源电流:133 mA to 400 mA 最大工作温度:+ 70 C |

发布紧急采购,3分钟左右您将得到回复。