- 您现在的位置:买卖IC网 > PDF目录16138 > TS-MAC-E2-U4 (Lattice Semiconductor Corporation)IP CORE ETH MAC TRI-SPEED EC/ECP PDF资料下载

参数资料

| 型号: | TS-MAC-E2-U4 |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 5/66页 |

| 文件大小: | 0K |

| 描述: | IP CORE ETH MAC TRI-SPEED EC/ECP |

| 标准包装: | 1 |

| 系列: | * |

| 其它名称: | TSMACE2U4 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

�� �

�

Chapter� 1:�

�Introduction�

�This� document� provides� technical� information� about� the� Lattice� 10/100/1G� Tri-Speed� Ethernet� Media� Access� Con-�

�troller� (TSMAC)� IP� core.�

�The� TSMAC� IP� core� supports� the� ability� to� transmit� and� receive� data� between� a� host� processor� and� an� Ethernet�

�network.� The� main� function� of� the� Ethernet� MAC� is� to� ensure� that� the� Media� Access� rules� specified� in� the� 802.3�

�IEEE� standard� are� met� while� transmitting� a� frame� of� data� over� Ethernet.� On� the� receiving� side,� the� Ethernet� MAC�

�extracts� the� different� components� of� a� frame� and� transfers� them� to� higher� applications� through� the� FIFO� interface.�

�The� TSMAC� IP� core� comes� with� the� following� documentation� and� files:�

�?� Protected� netlist/database�

�?� Behavioral� RTL� simulation� model�

�?� Source� files� for� instantiating� and� evaluating� the� core�

�Quick� Facts�

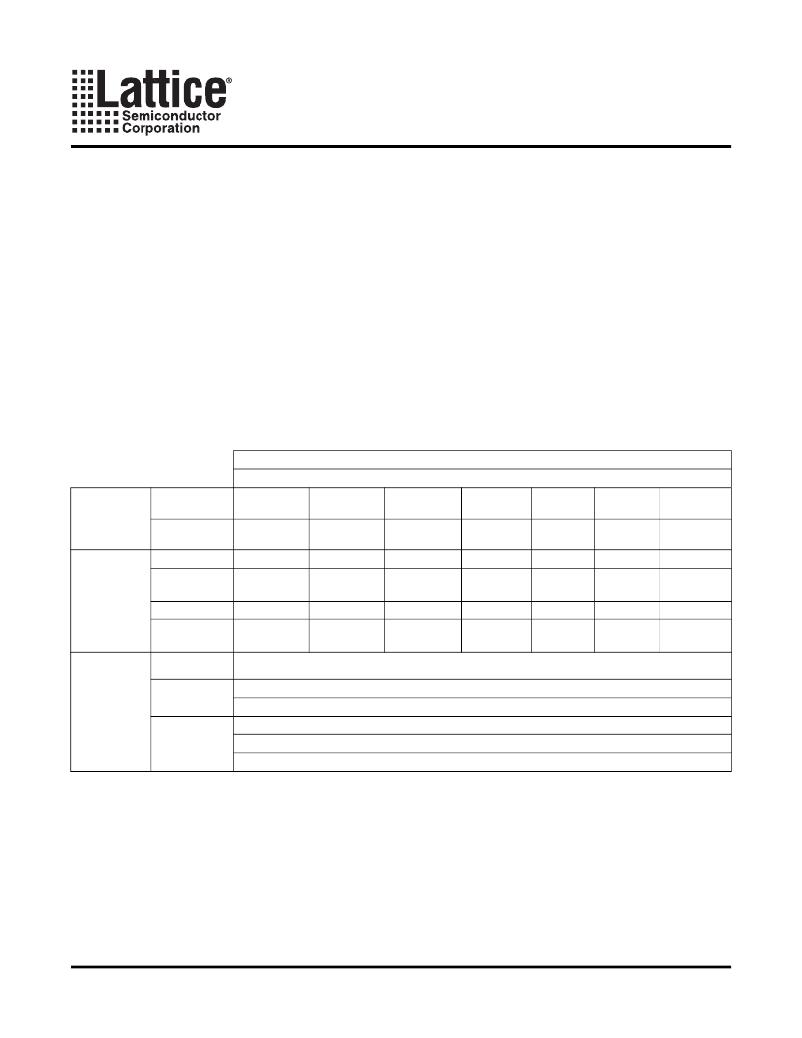

��Table� 1-1.� TSMAC� IP� Core� Quick� Facts�

�TSMAC� IP� Configuration�

�Across� all� configuration� options� (Classic,� Gigabit,� SGMII,� MIIM)� 1�

�Core�

�FPGA� Families�

�Supported�

�LatticeEC� TM�

�Lattice� ECP� TM�

�Lattice� ECP2� TM� LatticeECP2M� TM� LatticeECP3� TM� LatticeXP� TM�

�LatticeXP2� TM�

�LatticeSC� TM�

�LatticeSCM�

�Requirements�

�Minimal� Device�

�Needed�

�Data� Path� Width�

�LFEC3E-�

�5F100C�

�8�

�LFE2-6E-�

�5F144CES�

�8�

�LFE2M20-�

�5F256CES�

�8�

�LFE3-17E-�

�6FN256CES�

�8�

�LFXP6C-�

�5F144CES�

�8�

�LFXP2-5E-�

�6F132CES�

�8�

�LFSC3GA15�

�E-5F256CES�

�8�

�Registers�

�Resource�

�Utilization�

�LUTs� 2�

�sysMEM� EBRs�

�2�

�2�

�1600-2100�

�1-2�

�1100-1400�

�1600-2200�

�1-2�

�1100-1400�

�1600-2200�

�1-2�

�1100-1400�

�1500-2100�

�1-2�

�1100-1400�

�1600-�

�2100�

�1-2�

�1100-�

�1400�

�1600-2200�

�1-2�

�1100-1400�

�1600-2200�

�1-2�

�1100-1400�

�Lattice� ?�

�Implementation�

�Diamond� ?� 1.0� or� ipLEVER� ?� 8.1�

�Design� Tool�

�Support�

�Synthesis�

�Simulation�

�Synopsys� ?� Synplify� ?� Pro� for� Lattice� D-2009.12L-1�

�Mentor� Graphics� ?� Precision� ?� RTL�

�Aldec� Active-HDL� ?� 8.1� Lattice� Edition� (Verilog� and� VHDL)�

�Mentor� Graphics� ?� ModelSim� ?� 6.3f� SE� (Verilog� only)�

�Cadence� ?� NC-Verilog� ?� (Linux� only)�

�1)� The� SGMII� Easy� Connect� option� is� only� available� on� device� families� with� SERDES� I/O.�

�2)� The� leading� number� (before� the� dash)� represents� the� TSMAC� in� Gigabit� configuration� option� without� the� MIIM� module.� The� lagging� number�

�(after� the� dash)� represents� the� TSMAC� in� Classic� configuration� option� with� MIIM� module� included.� The� numbers� for� SGMII� Easy� Connect�

�configuration� option� with� MIIM� modules� are� the� same� as� the� lagging� numbers.�

�IPUG51_03.0,� December� 2010�

�5�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| IMC1210ER6R8K | INDUCTOR WW 6.8UH 10% 1210 |

| IMC1210ER5R6K | INDUCTOR WW 5.6UH 10% 1210 |

| IMC1210ER4R7K | INDUCTOR WW 4.7UH 10% 1210 |

| IMC1210ER3R9K | INDUCTOR WW 3.9UH 10% 1210 |

| IMC1210ER3R3K | INDUCTOR WW 3.3UH 10% 1210 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TS-MAC-E2-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-U3 | 功能描述:开发软件 Tri-Speed ethernet MAC RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-U4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TS-MAC-E3-UT4 | 功能描述:开发软件 ETHERNET MAC TRI-SPEED RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| TSMACP2U2 | 功能描述:以太网模块 TriSpd Ethernet MAC RoHS:否 制造商:Lantronix 产品:Device Servers 数据速率:300 bps to 921.6 kbps, 10 Mbps, 100 Mbps 接口类型:Ethernet, Serial 工作电源电压:5 V to 15 V 工作电源电流:133 mA to 400 mA 最大工作温度:+ 70 C |

发布紧急采购,3分钟左右您将得到回复。