- 您现在的位置:买卖IC网 > PDF目录68559 > W9412G2CB-5 (WINBOND ELECTRONICS CORP) 4M X 32 DDR DRAM, 0.6 ns, PBGA144 PDF资料下载

参数资料

| 型号: | W9412G2CB-5 |

| 厂商: | WINBOND ELECTRONICS CORP |

| 元件分类: | DRAM |

| 英文描述: | 4M X 32 DDR DRAM, 0.6 ns, PBGA144 |

| 封装: | 12 X 12 MM, 1.40 MM HEIGHT, ROHS COMPLIANT, LFBGA-144 |

| 文件页数: | 8/49页 |

| 文件大小: | 1936K |

| 代理商: | W9412G2CB-5 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

W9412G2CB

Publication Release Date:Jul. 07, 2008

- 16 -

Revision A11

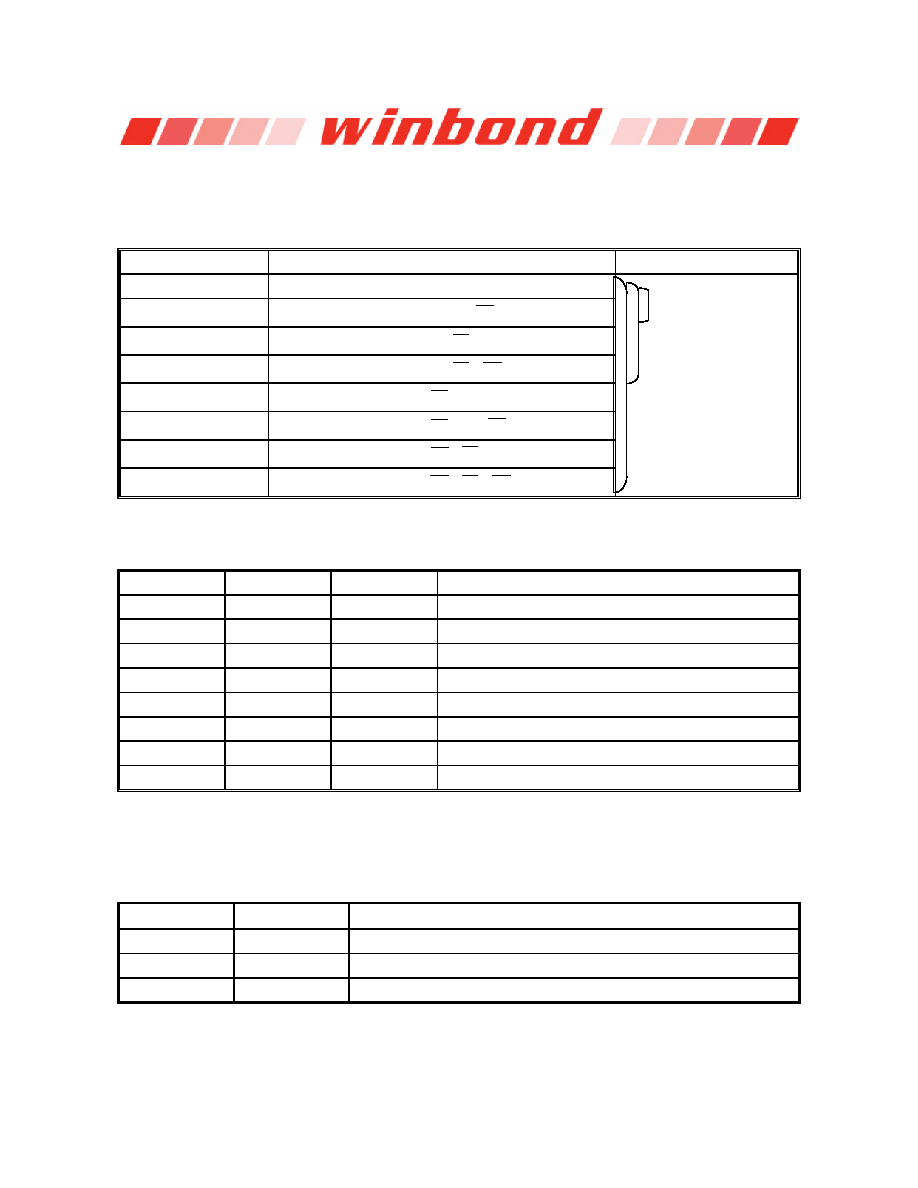

Addressing Sequence of Interleave Mode

A Column access is started from the inputted column address and is performed by

interleaving the address bits in the sequence shown as the following.

Address Sequence for Interleave Mode

DATA

ACCESS ADDRESS

BURST LENGTH

Data 0

A8 A7 A6 A5 A4 A3 A2 A1 A0

2 words

Data 1

A8 A7 A6 A5 A4 A3 A2 A1 A0

Data 2

A8 A7 A6 A5 A4 A3 A2 A1 A0

4 words

Data 3

A8 A7 A6 A5 A4 A3 A2 A1 A0

Data 4

A8 A7 A6 A5 A4 A3 A2 A1 A0

8 words

Data 5

A8 A7 A6 A5 A4 A3 A2 A1 A0

Data 6

A8 A7 A6 A5 A4 A3 A2 A1 A0

Data 7

A8 A7 A6 A5 A4 A3 A2 A1 A0

7.10.3 CAS Latency field (A6 to A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first

data read. The minimum values of CAS Latency depend on the frequency of CLK.

A6

A5

A4

CAS LATENCY

0

Reserved

0

1

Reserved

0

1

0

2

0

1

3

1

0

Reserved

1

0

1

Reserved

1

0

2.5

1

Reserved

7.10.4 DLL Reset bit (A8)

This bit is used to reset DLL. When the A8 bit is “1”, DLL is reset.

7.10.5 Mode Register /Extended Mode register change bits (BA0, BA1)

These bits are used to select MRS/EMRS.

BA1

BA0

A11

A0

0

Regular MRS Cycle

0

1

Extended MRS Cycle

1

x

Reserved

相关PDF资料 |

PDF描述 |

|---|---|

| W9412G6IH-4 | 8M X 16 DDR DRAM, 0.65 ns, PDSO66 |

| W942508AH-8 | 32M X 8 DDR DRAM, 0.8 ns, PDSO66 |

| W942516AH-6 | 16M X 16 DDR DRAM, 0.7 ns, PDSO66 |

| W942516CH-75 | 16M X 16 DDR DRAM, 0.75 ns, PDSO66 |

| W9425G6DH-6F | 16M X 16 DDR DRAM, 0.7 ns, PDSO66 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| W9412G2IB | 制造商:WINBOND 制造商全称:Winbond 功能描述:1M × 4 BANKS × 32 BITS GDDR SDRAM |

| W9412G2IB4 | 制造商:WINBOND 制造商全称:Winbond 功能描述:Double Data Rate architecture; two data transfers per clock cycle |

| W9412G2IB-5 | 制造商:Winbond Electronics Corp 功能描述:8*16 DDR1 |

| W9412G6CH | 制造商:WINBOND 制造商全称:Winbond 功能描述:2M 】 4 BANKS 】 16 BITS DDR SDRAM |

| W9412G6IH | 制造商:WINBOND 制造商全称:Winbond 功能描述:2M × 4 BANKS × 16 BITS DDR SDRAM |

发布紧急采购,3分钟左右您将得到回复。