- 您现在的位置:买卖IC网 > PDF目录21989 > XC2S50-5PQG208C (Xilinx Inc)IC SPARTAN-II FPGA 50K 208-PQFP PDF资料下载

参数资料

| 型号: | XC2S50-5PQG208C |

| 厂商: | Xilinx Inc |

| 文件页数: | 17/99页 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-II FPGA 50K 208-PQFP |

| 标准包装: | 24 |

| 系列: | Spartan®-II |

| LAB/CLB数: | 384 |

| 逻辑元件/单元数: | 1728 |

| RAM 位总计: | 32768 |

| 输入/输出数: | 140 |

| 门数: | 50000 |

| 电源电压: | 2.375 V ~ 2.625 V |

| 安装类型: | 表面贴装 |

| 工作温度: | 0°C ~ 85°C |

| 封装/外壳: | 208-BFQFP |

| 供应商设备封装: | 208-PQFP(28x28) |

| 产品目录页面: | 599 (CN2011-ZH PDF) |

| 其它名称: | 122-1320 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

24

R

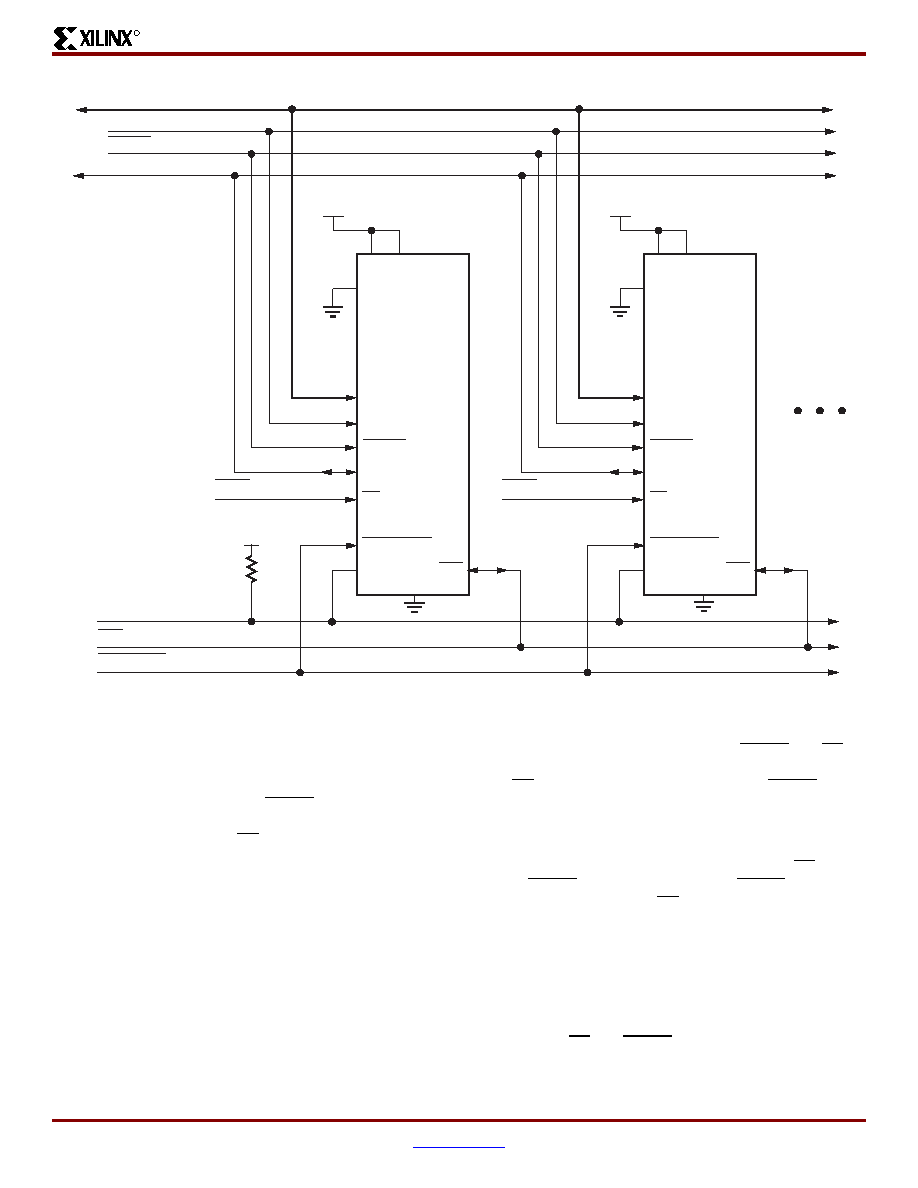

Multiple Spartan-II FPGAs can be configured using the

Slave Parallel mode, and be made to start-up

simultaneously. To configure multiple devices in this way,

wire the individual CCLK, Data, WRITE, and BUSY pins of

all the devices in parallel. The individual devices are loaded

separately by asserting the CS pin of each device in turn

and writing the appropriate data. Sync-to-DONE start-up

timing is used to ensure that the start-up sequence does not

begin until all the FPGAs have been loaded. See "Start-up,"

Write

When using the Slave Parallel Mode, write operations send

packets of byte-wide configuration data into the FPGA.

Figure 19, page 25 shows a flowchart of the write sequence

used to load data into the Spartan-II FPGA. This is an

expansion of the "Load Configuration Data Frames" block in

Figure 11, page 18. The timing for write operations is shown

For the present example, the user holds WRITE and CS

Low throughout the sequence of write operations. Note that

when CS is asserted on successive CCLKs, WRITE must

remain either asserted or de-asserted. Otherwise an abort

will be initiated, as in the next section.

1.

Drive data onto D0-D7. Note that to avoid contention,

the data source should not be enabled while CS is Low

and WRITE is High. Similarly, while WRITE is High, no

more than one device’s CS should be asserted.

2.

On the rising edge of CCLK: If BUSY is Low, the data is

accepted on this clock. If BUSY is High (from a previous

write), the data is not accepted. Acceptance will instead

occur on the first clock after BUSY goes Low, and the

data must be held until this happens.

3.

Repeat steps 1 and 2 until all the data has been sent.

4.

De-assert CS and WRITE.

Figure 18: Slave Parallel Configuration Circuit Diagram

M1 M2

M0

D0:D7

CCLK

WRITE

BUSY

CS

PROGRAM

DONEINIT

CCLK

DATA[7:0]

WRITE

BUSY

CS(0)

330

Ω

Spartan-II

FPGA

DONE

INIT

PROGRAM

M1 M2

M0

D0:D7

CCLK

WRITE

BUSY

CS

PROGRAM

DONEINIT

CS(1)

Spartan-II

FPGA

DS001_18_060608

GND

相关PDF资料 |

PDF描述 |

|---|---|

| FMC13DRYN-S734 | CONN EDGECARD 26POS DIP .100 SLD |

| TACR336M010RTA | CAP TANT 33UF 10V 20% 0805 |

| XC3S250E-4VQG100C | IC SPARTAN-3E FPGA 250K 100VQFP |

| FMC13DRYH-S734 | CONN EDGECARD 26POS DIP .100 SLD |

| XC3S100E-4TQG144I | IC FPGA SPARTAN-3E 100K 144-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XC2S50-5PQG208I | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 50K GATES 1728 CELLS 263MHZ 2.5V 208PQFP - Trays |

| XC2S50-5TQ144C | 功能描述:IC FPGA 2.5V 384 CLB'S 144-TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-II 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC2S50-5TQ144C-ES | 制造商:Xilinx 功能描述:2S50-5TQ144C-ES |

| XC2S50-5TQ144I | 功能描述:IC FPGA 2.5V I-TEMP 144-TQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-II 标准包装:40 系列:Spartan® 6 LX LAB/CLB数:3411 逻辑元件/单元数:43661 RAM 位总计:2138112 输入/输出数:358 门数:- 电源电压:1.14 V ~ 1.26 V 安装类型:表面贴装 工作温度:-40°C ~ 100°C 封装/外壳:676-BGA 供应商设备封装:676-FBGA(27x27) |

| XC2S50-5TQG144C | 功能描述:IC SPARTAN-II FPGA 50K 144-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - FPGA(现场可编程门阵列) 系列:Spartan®-II 标准包装:60 系列:XP LAB/CLB数:- 逻辑元件/单元数:10000 RAM 位总计:221184 输入/输出数:244 门数:- 电源电压:1.71 V ~ 3.465 V 安装类型:表面贴装 工作温度:0°C ~ 85°C 封装/外壳:388-BBGA 供应商设备封装:388-FPBGA(23x23) 其它名称:220-1241 |

发布紧急采购,3分钟左右您将得到回复。