参数资料

| 型号: | XRD98L61AIV-F |

| 厂商: | Exar Corporation |

| 文件页数: | 16/38页 |

| 文件大小: | 0K |

| 描述: | IC CCD DIGITIZER 12BIT 48TQFP |

| 标准包装: | 250 |

| 位数: | 12 |

| 通道数: | 1 |

| 电压 - 电源,模拟: | 2.7 V ~ 3.6 V |

| 电压 - 电源,数字: | 2.7 V ~ 3.6 V |

| 封装/外壳: | 48-TQFP |

| 供应商设备封装: | 48-TQFP(7x7) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页当前第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

23

Rev. 2.00

XRD98L61

CALIBRATION OPTIONS

Fast Cal

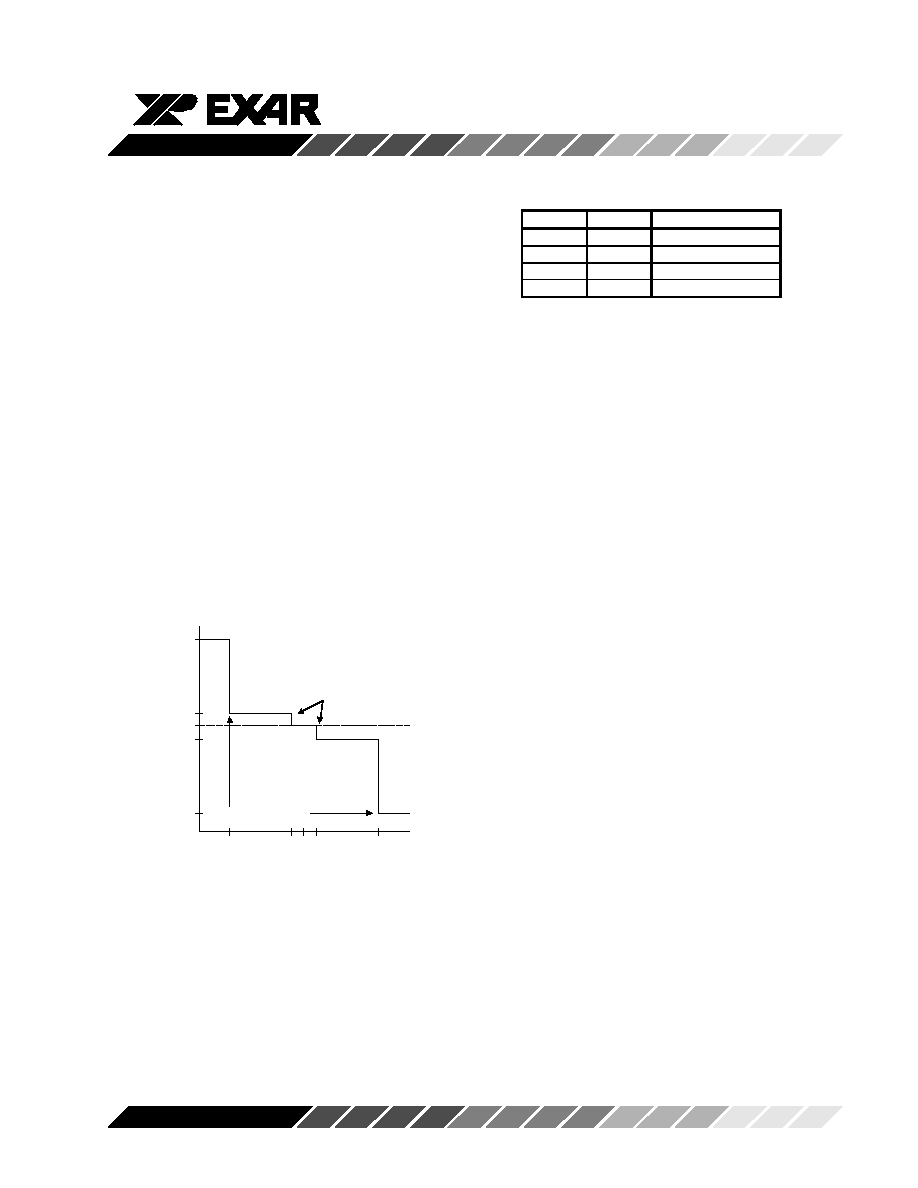

The purpose of this option is to reduce the amount of

time required for initial convergence of the calibration

feedback system. The feedback system is designed to

have a slow response time to avoid introducing image

artifacts. The slow response time is achieved by

averaging many OB pixels and by limiting the Fine

accumulator changes to ± 1 count at a time (FDAC lsb

= ADC lsb). The FastCal option maintains this slow

response while the difference between the averaged

ADC data and the Offset Code is small, but when the

difference is larger than ±128 lsb’s, the coarse accu-

mulator takes a step. The actual step size depends on

the PGA Gain code, and is set such that the step will

cause no more than a 128 LSB change in the ADC

output.

To activate the FastCal mode ,write a “1” to the FastCal

bit in the Calibration register. By default, the FastCal

mode is active.

Difference [ADC lsb's]

O

ff

s

e

t

A

d

ju

s

tm

e

n

t

[A

D

C

L

S

B

s

]

0

-1

+1

-128

+128

0

+0.5

-0.5

Fine DAC Steps

Coarse DAC steps

Figure 11. Calibration in FastCal

(Speed Up) Mode

DNS[1]

DNS[0]

DNS Filter Width

0

OFF (default)

0

1

Narrow

1

0

Medium

1

Wide

Digital Noise Suppression (DNS Filter)

The purpose of this option is to eliminate small

changes in the Black Level offset by making the

calibration system less sensitive to small changes in

the measured offset. In this mode, the user has the

option of selecting from three filter settings;see Table 5.

Table 5. DNS Threshold Programming

To activate the Digital Noise Suppression mode, write

to the DNS[1:0] bits in the Calibration register.By

default, the Digital Noise Suppression is ON and set to

the wide filter width.

Hold Mode

The purpose of this mode is to prevent any changes in

the Fine or Coarse accumulators. This mode is in-

tended to optimize digital still camera applications

(DSC). The idea is to first run the calibration normally

so the Fine and Coarse accumulators converge on the

correct values to achieve the programmed Offset

Code. Then, just before acquiring the final image data,

activate the Hold mode. This will ensure the black level

offset of the CDS/PGA does not change while the final

image is being transferred out of the CCD. Once the

image has been acquired from the CCD, turn off the

Hold mode so the chip can continue to compensate for

any changes in offset due to temperature drift or other

effects.

To activate the Hold mode, write a “1” to the Hold bit in

the Calibration register. By default, the Hold mode is

not active.

相关PDF资料 |

PDF描述 |

|---|---|

| XRD98L62ACV-F | IC CCD DIGITIZER 12BIT 48TQFP |

| XRD98L63AIV-F | IC CCD DIGITIZER 12BIT 48TQFP |

| XRT71D00IQ-F | IC JITTER ATTENUATOR SGL 32TQFP |

| XRT71D03IV-F | IC JITTER ATTENUATOR 3CH 64TQFP |

| XRT71D04IV | IC JITTER ATTENUATOR 4CH 80TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| XRD98L61EVAL | 功能描述:数据转换 IC 开发工具 Eval Board for XRD98L61AIV RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| XRD98L61ZEVAL | 功能描述:数据转换 IC 开发工具 Eval Board (Solder) XRD98L61AIV RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| XRD98L62 | 制造商:EXAR 制造商全称:EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L62ACV | 制造商:EXAR 制造商全称:EXAR 功能描述:CCD Image Digitizers with CDS, PGA and 12-Bit A/D |

| XRD98L62ACV-F | 功能描述:视频 IC RoHS:否 制造商:Fairchild Semiconductor 工作电源电压:5 V 电源电流:80 mA 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-28 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。