- 您现在的位置:买卖IC网 > PDF目录293971 > 5962-9205805QXA (TEXAS INSTRUMENTS INC) 32-BIT, 60 MHz, OTHER DSP, CPGA141 PDF资料下载

参数资料

| 型号: | 5962-9205805QXA |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 32-BIT, 60 MHz, OTHER DSP, CPGA141 |

| 封装: | STAGGERED, CERAMIC, PGA-141 |

| 文件页数: | 17/54页 |

| 文件大小: | 1033K |

| 代理商: | 5962-9205805QXA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

SMJ320C31, SMJ320LC31, SMQ320LC31

DIGITAL SIGNAL PROCESSORS

SGUS026G APRIL 1998 REVISED SEPTEMBER 2006

24

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

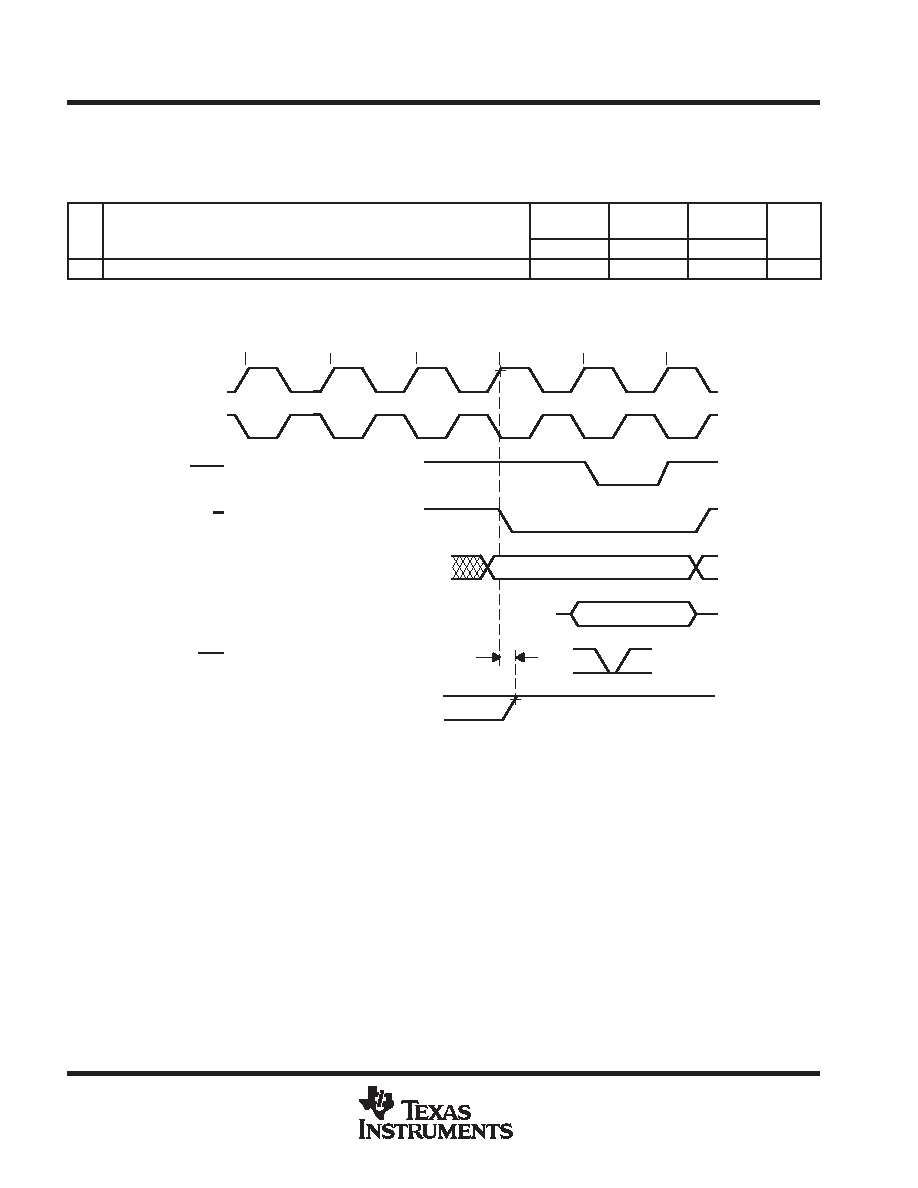

XF0 timing when executing STFI and STII

The following table defines the timing parameters for the XF0 pin during execution of STFI or STII.

timing for XF0 when executing STFI or STII (see Figure 18)

NO.

’C31-40

’LC31-40

’C31-50

’C31-60

UNIT

NO.

MIN

MAX

MIN

MAX

MIN

MAX

UNIT

28

td(H3H-XF0H)

Delay time, H3 high to XF0 high

13

12

11

ns

XF0 is always set high at the beginning of the execute phase of the interlock-store instruction. When no pipeline conflicts occur, the address of

the store is also driven at the beginning of the execute phase of the interlock-store instruction. However, if a pipeline conflict prevents the store

from executing, the address of the store will not be driven until the store can execute.

H3

H1

STRB

R/W

A

D

RDY

XF0 Pin

Fetch

STFI or STII

Read

Execute

28

Decode

Figure 18. Timing for XF0 When Executing an STFI or STII

相关PDF资料 |

PDF描述 |

|---|---|

| 5962-9309101HYA | EEPROM 5V MODULE, CDIP32 |

| 5962-9315302MXX | 4K X 9 MULTI-PORT SRAM, 25 ns, CQCC |

| 596287663012X | ACT SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, CQCC20 |

| 5962D0053605QYX | 512K X 8 STANDARD SRAM, 20 ns, CDFP36 |

| 5962D1022901QXC | 64M X 40 SYNCHRONOUS DRAM, 5.4 ns, CQFP128 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962-9205805QYA | 制造商:Texas Instruments 功能描述:DSP FLOATING PT 32BIT 60MHZ 30MIPS 132CFPAK - Rail/Tube |

| 596292062012MYC | 制造商:ALTERA 功能描述:EPM5192GM883B |

| 5962-92062012MYC | 制造商:ALTERA 功能描述:EPM5192GM883B |

| 5962-9206201MYC | 制造商:Cypress Semiconductor 功能描述:CPLD 192 Macro Cells 0.8um (CMOS) Technology 5V 84-Pin Windowed PGA |

| 5962-9206202MYC | 制造商:e2v Aerospace & Defense 功能描述:CPLD, UV ERASABLE, 192-MACROCELL, 30 NS PROP. DELAY TIME |

发布紧急采购,3分钟左右您将得到回复。