- 您现在的位置:买卖IC网 > PDF目录293971 > 5962-9205805QXA (TEXAS INSTRUMENTS INC) 32-BIT, 60 MHz, OTHER DSP, CPGA141 PDF资料下载

参数资料

| 型号: | 5962-9205805QXA |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 32-BIT, 60 MHz, OTHER DSP, CPGA141 |

| 封装: | STAGGERED, CERAMIC, PGA-141 |

| 文件页数: | 52/54页 |

| 文件大小: | 1033K |

| 代理商: | 5962-9205805QXA |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页第53页第54页

SMJ320C31, SMJ320LC31, SMQ320LC31

DIGITAL SIGNAL PROCESSORS

SGUS026G APRIL 1998 REVISED SEPTEMBER 2006

7

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

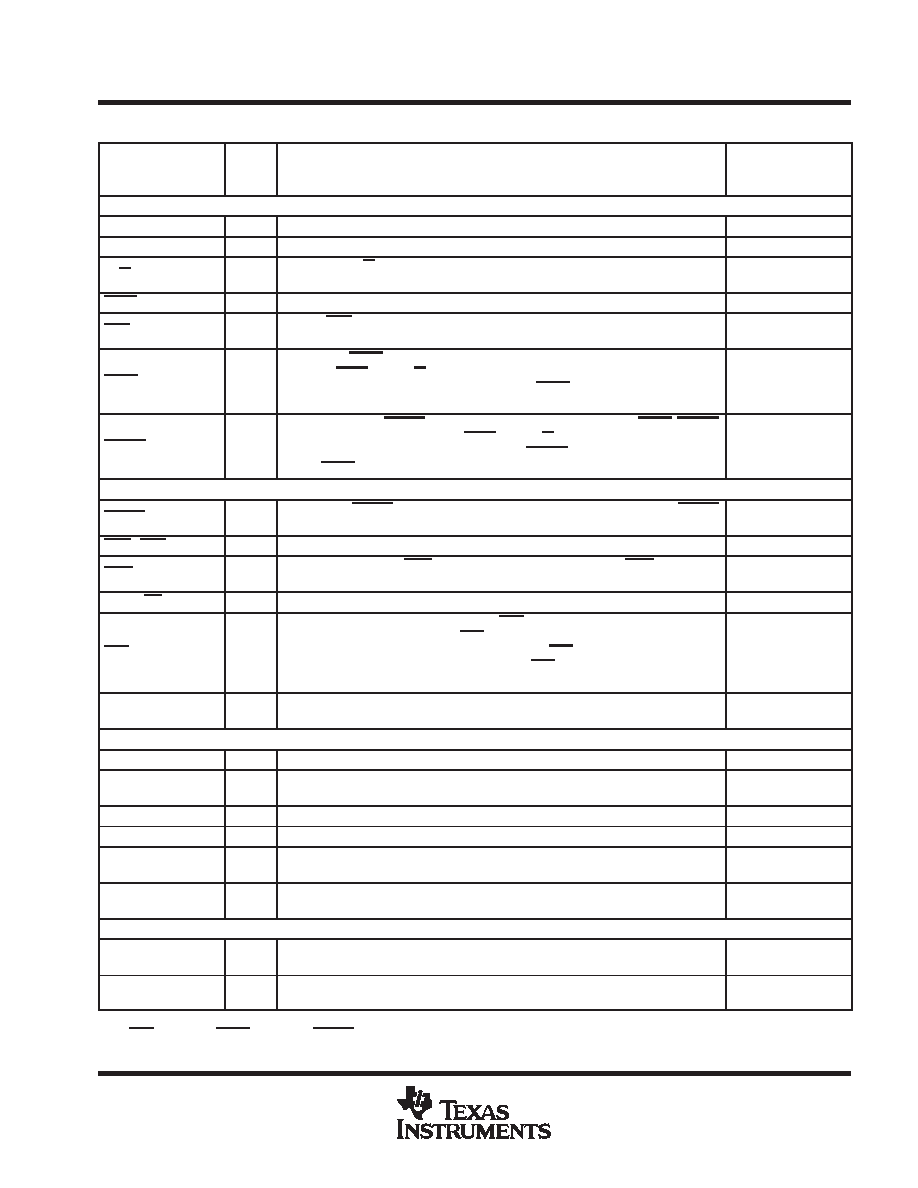

Terminal Functions

TERMINAL

TYPE

DESCRIPTION

CONDITIONS

WHEN

NAME

QTY

TYPE

DESCRIPTION

WHEN

SIGNAL IS Z TYPE

PRIMARY-BUS INTERFACE

D31 D0

32

I/O/Z

32-bit data port

S

H

R

A23 A0

24

O/Z

24-bit address port

S

H

R

R/W

1

O/Z

Read / write. R/ W is high when a read is performed and low when a write is performed

over the parallel interface.

S

H

R

STRB

1

O/Z

External-access strobe

S

H

RDY

1

I

Ready. RDY indicates that the external device is prepared for a transaction

completion.

HOLD

1

I

Hold. When HOLD is a logic low, any ongoing transaction is completed. A23 A0,

D31 D0, STRB, and R / W are placed in the high-impedance state and all transac-

tions over the primary-bus interface are held until HOLD becomes a logic high or until

the NOHOLD bit of the primary-bus-control register is set.

HOLDA

1

O/Z

Hold acknowledge. HOLDA is generated in response to a logic low on HOLD. HOLDA

indicates that A23 A0, D31 D0, STRB, and R / W are in the high-impedance state

and that all transactions over the bus are held. HOLDA is high in response to a logic

high of HOLD or the NOHOLD bit of the primary-bus-control register is set.

S

CONTROL SIGNALS

RESET

1

I

Reset. When RESET is a logic low, the device is in the reset condition. When RESET

becomes a logic high, execution begins from the location specified by the reset vector.

INT3 INT0

4

I

External interrupts

IACK

1

O/Z

Interrupt acknowledge. IACK is generated by the IACK instruction. IACK can be used

to indicate the beginning or the end of an interrupt-service routine.

S

MCBL / MP

1

I

Microcomputer boot-loader / microprocessor mode-select

SHZ

1

I

Shutdown high impedance. When active, SHZ shuts down the device and places all

pins in the high-impedance state. SHZ is used for board-level testing to ensure that

no dual-drive conditions occur. CAUTION: A low on SHZ corrupts the device memory

and register contents. Reset the device with SHZ high to restore it to a known

operating condition.

XF1, XF0

2

I/O/Z

External flags. XF1 and XF0 are used as general-purpose I / Os or to support

interlocked processor instruction.

S

R

SERIAL PORT 0 SIGNALS

CLKR0

1

I/O/Z

Serial port 0 receive clock. CLKR0 is the serial shift clock for the serial port 0 receiver.

S

R

CLKX0

1

I/O/Z

Serial port 0 transmit clock. CLKX0 is the serial shift clock for the serial port 0

transmitter.

S

R

DR0

1

I/O/Z

Data-receive. Serial port 0 receives serial data on DR0.

S

R

DX0

1

I/O/Z

Data-transmit output. Serial port 0 transmits serial data on DX0.

S

R

FSR0

1

I/O/Z

Frame-synchronization pulse for receive. The FSR0 pulse initiates the data-receive

process using DR0.

S

R

FSX0

1

I/O/Z

Frame-synchronization pulse for transmit. The FSX0 pulse initiates the data-transmit

process using DX0.

S

R

TIMER SIGNALS

TCLK0

1

I/O/Z

Timer clock 0. As an input, TCLK0 is used by timer 0 to count external pulses. As an

output, TCLK0 outputs pulses generated by timer 0.

S

TCLK1

1

I/O/Z

Timer clock 1. As an input, TCLK0 is used by timer 1 to count external pulses. As an

output, TCLK1 outputs pulses generated by timer 1.

S

I = input, O = output, Z = high-impedance state

S = SHZ active, H = HOLD active, R = RESET active

相关PDF资料 |

PDF描述 |

|---|---|

| 5962-9309101HYA | EEPROM 5V MODULE, CDIP32 |

| 5962-9315302MXX | 4K X 9 MULTI-PORT SRAM, 25 ns, CQCC |

| 596287663012X | ACT SERIES, 8-BIT TRANSCEIVER, TRUE OUTPUT, CQCC20 |

| 5962D0053605QYX | 512K X 8 STANDARD SRAM, 20 ns, CDFP36 |

| 5962D1022901QXC | 64M X 40 SYNCHRONOUS DRAM, 5.4 ns, CQFP128 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 5962-9205805QYA | 制造商:Texas Instruments 功能描述:DSP FLOATING PT 32BIT 60MHZ 30MIPS 132CFPAK - Rail/Tube |

| 596292062012MYC | 制造商:ALTERA 功能描述:EPM5192GM883B |

| 5962-92062012MYC | 制造商:ALTERA 功能描述:EPM5192GM883B |

| 5962-9206201MYC | 制造商:Cypress Semiconductor 功能描述:CPLD 192 Macro Cells 0.8um (CMOS) Technology 5V 84-Pin Windowed PGA |

| 5962-9206202MYC | 制造商:e2v Aerospace & Defense 功能描述:CPLD, UV ERASABLE, 192-MACROCELL, 30 NS PROP. DELAY TIME |

发布紧急采购,3分钟左右您将得到回复。