- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6531D-IM/F (TERIDIAN SEMICONDUCTOR CORP) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 PDF资料下载

参数资料

| 型号: | 71M6531D-IM/F |

| 厂商: | TERIDIAN SEMICONDUCTOR CORP |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 封装: | LEAD FREE, QFN-68 |

| 文件页数: | 104/120页 |

| 文件大小: | 2477K |

| 代理商: | 71M6531D-IM/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页当前第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页

Data Sheet 71M6531D/F-71M6532D/F

FDS 6531/6532 005

84

2005-2010 TERIDIAN Semiconductor Corporation

v1.3

Name

Location

Reset

Wake

Dir

Description

MUX_ALT

2005[2]

0

R/W

The MPU asserts this bit when it wishes the MUX to perform ADC conversions on an

alternate set of inputs.

If CHOP_E[1:0] is 00, MUX_ALT is automatically asserted once per sumcycle, when

XFER_BUSY falls.

MUX_DIV[3:0]

209D[3:0]

0

R/W

The number of states in the input multiplexer.

MUX_SYNC_E

2020[7]

0

R/W

When set, SEG7 outputs MUX_SYNC. Otherwise, SEG7 is an LCD pin.

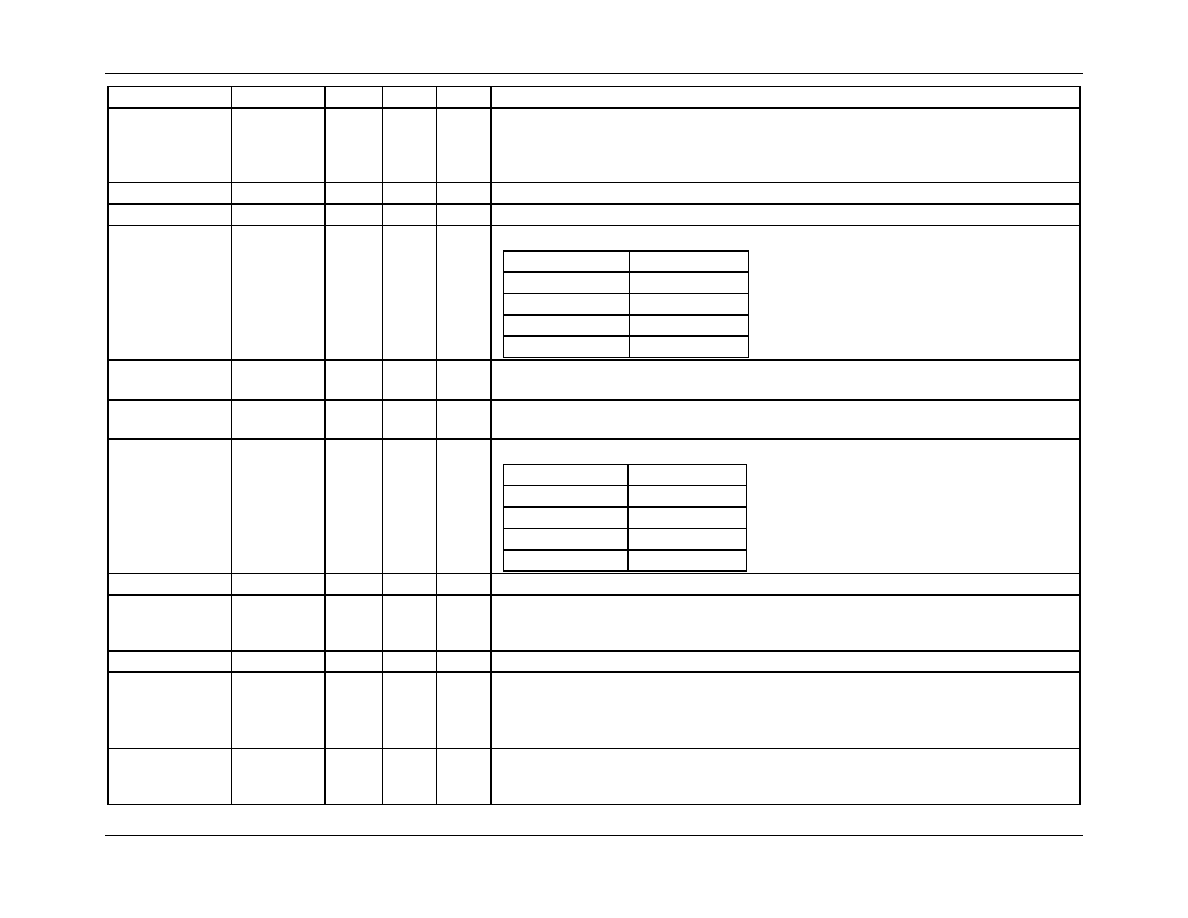

OPT_FDC[1:0]

2007[1:0]

0

R/W

Selects the modulation duty cycle for OPT_TX.

OPT_FDC[1:0]

Function

00

50% Low

01

25% Low

10

12.5% Low

11

6.25% Low

OPT_RXDIS

2008[5]

0

R/W

Configures OPT_RX to an analog input to the optical UART comparator or as a digital

input/output, DIO1: 0 = OPT_RX, 1 = DIO1.

OPT_RXINV

2008[4]

0

R/W

Inverts the result from the OPT_RX comparator when 1. Affects only the UART input.

Has no effect when OPT_RX is used as a DIO input.

OPT_TXE[1:0]

2007[7:6]

00

R/W

Configures the OPT_TX output pin.

OPT_TXE[1:0]

Function

00

OPT_TX

01

DIO2

10

WPULSE

11

RPULSE

OPT_TXINV

2008[0]

0

R/W

Inverts OPT_TX when 1. This inversion occurs before modulation.

OPT_TXMOD

2008[1]

0

R/W

Enables modulation of OPT_TX. When OPT_TXMOD is set, OPT_TX is modulated

when it would otherwise have been zero. The modulation is applied after any inversion

caused by OPT_TXINV.

PLL_OK

2003[6]

0

R

Indicates that system power is present and the clock generation PLL is settled.

PLS_MAXWIDTH

[7:0]

2080[7:0]

FF

R/W

Determines the maximum width of the pulse (low going pulse).

The maximum pulse width is (2*PLS_MAXWIDTH + 1)*TI. Where TI is PLS_INTERVAL.

If PLS_INTERVAL = 0, TI is the sample time (397 s). If set to 255, pulse width control

is disabled and pulses are output with a 50% duty cycle.

PLS_INTERVAL

[7:0]

2081[7:0]

0

R/W

For PULSE_W and PULSE_V only: If the FIFO is used, PLS_INTERVAL must be set to

81. If PLS_INTERVAL = 0, the FIFO is not used and pulses are output as soon as the

CE issues them.

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6532F-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6534-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6531D-IMR/F | 功能描述:计量片上系统 - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531D-IMR/F1 | 功能描述:计量片上系统 - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531D-IMR/F2 | 功能描述:计量片上系统 - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531F | 制造商:TERIDIAN 制造商全称:TERIDIAN 功能描述:Energy Meter IC |

| 71M6531F-DB | 功能描述:开发板和工具包 - 8051 71M6531F Demo Brd RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。