- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6531D-IM/F (TERIDIAN SEMICONDUCTOR CORP) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 PDF资料下载

参数资料

| 型号: | 71M6531D-IM/F |

| 厂商: | TERIDIAN SEMICONDUCTOR CORP |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 封装: | LEAD FREE, QFN-68 |

| 文件页数: | 69/120页 |

| 文件大小: | 2477K |

| 代理商: | 71M6531D-IM/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页当前第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页

Data Sheet 71M6531D/F-71M6532D/F

FDS 6531/6532 005

52

2005-2010 TERIDIAN Semiconductor Corporation

v1.3

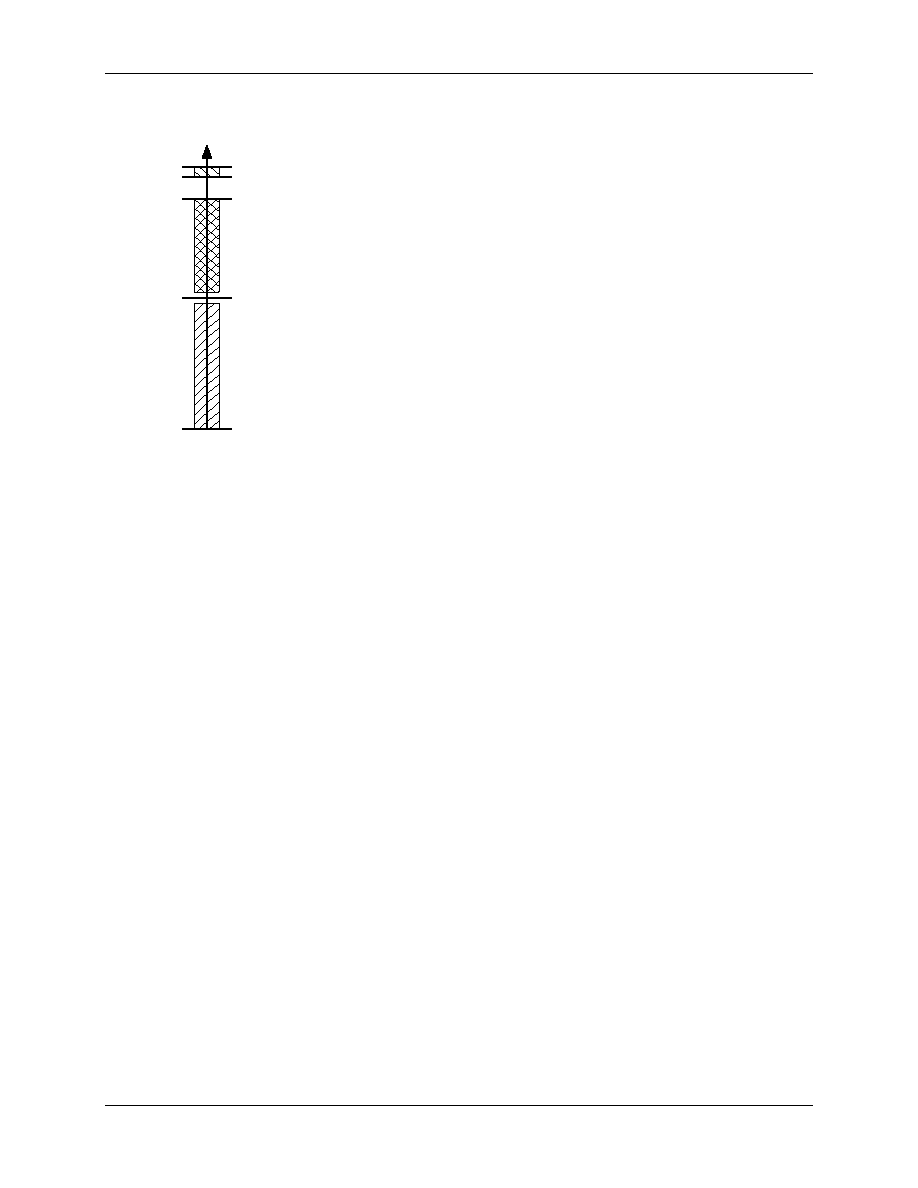

V3P3

V3P3 -

400mV

V3P3 - 10mV

VBIAS

0V

Battery

modes

Normal

operation,

WDT

enabled

WDT dis-

abled

V1

1.5.16 Hardware Watchdog Timer

An independent, robust, fixed-duration, watchdog timer (WDT) is included

in the 71M6531D/F and 71M6532D/F. It uses the RTC crystal oscillator as

its time base and must be refreshed by the MPU firmware at least every

1.5 seconds. When not refreshed on time, the WDT overflows and the part

is reset as if the RESET pin were pulled high, except that the I/O RAM bits

will be in the same state as after a wake-up from SLEEP or LCD modes

(see the I/O RAM description in Section 4.2 for a list of I/O RAM bit states

after RESET and wake-up). 4100 oscillator cycles (or 125 ms) after the

WDT overflow, the MPU will be launched from program address 0x0000.

A status bit, WD_OVF, is set when the WDT overflow occurs. This bit is

powered by the nonvolatile supply and can be read by the MPU when

WAKE rises to determine if the part is initializing after a WDT overflow

event or after a power-up. After it is read, the MPU firmware must clear

WD_OVF. The WD_OVF bit is also cleared by the RESET pin.

There is no internal digital state that deactivates the WDT.

Figure 17: Functions defined by V1

The WDT can be disabled by tying the V1 pin to V3P3 (see Figure 17). Of course, this also deactivates

V1 power fault detection. Since there is no method in firmware to disable the crystal oscillator or the

WDT, it is guaranteed that whatever state the part might find itself in, upon watchdog overflow, the part

will be reset to a known state.

Asserting ICE_E will also deactivate the WDT. This is the only method that will work in BROWNOUT

mode. In normal operation, the WDT is reset by periodically writing a one to the WDT_RST bit. The

watchdog timer is also reset when the internal signal WAKE = 0 (see Section 2.5 Wake-Up Behavior).

If enabled with the IEN_WD_NROVF bit in I/O RAM, an interrupt occurs roughly 1 ms before the WDT resets

the chip. This can be used to determine the cause of a WDT reset since it allows the code to log its state

(e.g. the current PC value, loop counters, flags, etc.) before a WDT reset occurs.

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6532F-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6534-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6531D-IMR/F | 功能描述:计量片上系统 - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531D-IMR/F1 | 功能描述:计量片上系统 - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531D-IMR/F2 | 功能描述:计量片上系统 - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531F | 制造商:TERIDIAN 制造商全称:TERIDIAN 功能描述:Energy Meter IC |

| 71M6531F-DB | 功能描述:开发板和工具包 - 8051 71M6531F Demo Brd RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。