- 您现在的位置:买卖IC网 > PDF目录68811 > 71M6531D-IM/F (TERIDIAN SEMICONDUCTOR CORP) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 PDF资料下载

参数资料

| 型号: | 71M6531D-IM/F |

| 厂商: | TERIDIAN SEMICONDUCTOR CORP |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, QCC68 |

| 封装: | LEAD FREE, QFN-68 |

| 文件页数: | 38/120页 |

| 文件大小: | 2477K |

| 代理商: | 71M6531D-IM/F |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页

Data Sheet 71M6531D/F-71M6532D/F

FDS 6531/6532 005

24

2005-2010 TERIDIAN Semiconductor Corporation

v1.3

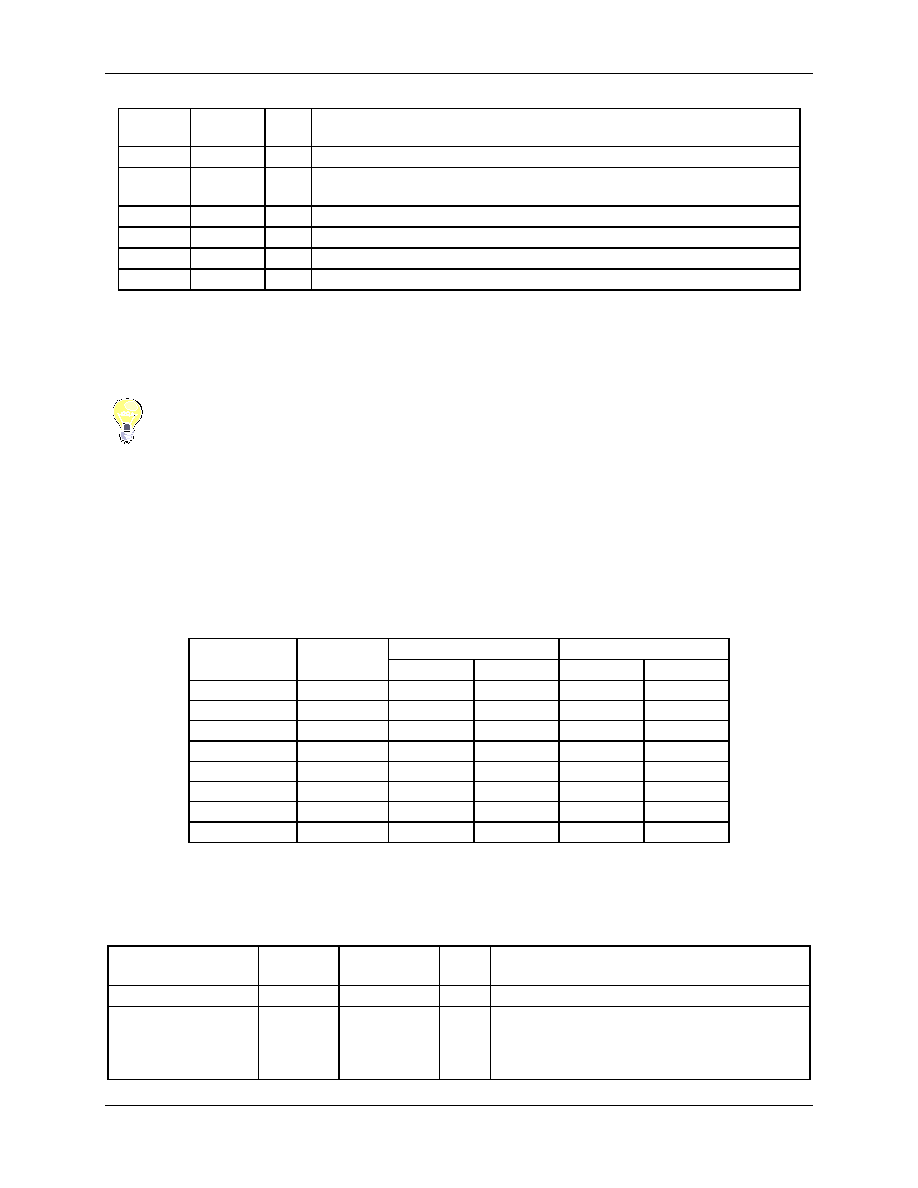

Table 12: Port Registers

Register

SFR

Address

R/W

Description

P0

0x80

R/W

Register for port 0 read and write operations.

DIR0

0xA2

R/W

Data direction register for port 0. Setting a bit to 1 indicates that the

corresponding pin is an output.

P1

0x90

R/W

Register for port 1 read and write operations.

DIR1

0x91

R/W

Data direction register for port 1.

P2

0xA0

R/W

Register for port 2 read and write operations.

DIR2

0xA1

R/W

Data direction register for port 2.

All DIO ports on the chip are bi-directional. Each of them consists of a Latch (SFR P0 to P2), an output

driver and an input buffer, therefore the MPU can output or read data through any of these ports. Even if

a DIO pin is configured as an output, the state of the pin can still be read by the MPU, for example when

counting pulses issued via DIO pins that are under CE control.

The technique of reading the status of or generating interrupts based on DIO pins configured as

outputs can be used to implement pulse counting.

Clock Stretching (CKCON[2:0], SFR 0x8E)

The CKCON[2:0] field defines the stretch memory cycles that could be used for MOVX instructions when

accessing slow external peripherals. The practical value of this register for the 71M653x is to guarantee

access to XRAM between CE, MPU, and SPI. The default setting of CKCON[2:0] (001) should not be

changed.Table 13 shows how the signals of the External Memory Interface change when stretch values

are set from 0 to 7. The widths of the signals are counted in MPU clock cycles. The post-reset state of

the CKCON[2:0] field (001), which is shown in bold in the table, performs the MOVX instructions with a

stretch value equal to 1.

Table 13: Stretch Memory Cycle Width

CKCON[2:0]

Stretch

Value

Read signal width

Write signal width

memaddr

memrd

memaddr

memwr

000

0

1

2

1

001

1

2

3

1

010

2

3

4

2

011

3

4

5

3

100

4

5

6

4

101

5

6

7

5

110

6

7

8

6

111

7

8

9

7

1.4.4

Special Function Registers (SFRs) Specific to the 71M6531D/F and 71M6532D/F

Table 14 shows the location and description of the SFRs specific to the 71M6531D/F and 71M6532D/F.

Table 14: 71M6531D/F and 71M6532D/F Specific SFRs

Register

(Alternate Name)

SFR

Address

Bit Field

Name

R/W

Description

EEDATA

0x9E

R/W

I

2C EEPROM interface data register.

EECTRL

0x9F

R/W

I

2C EEPROM interface control register. See

Section 1.5.14 EEPROM Interface for a

description of the command and status bits

available for EECTRL.

相关PDF资料 |

PDF描述 |

|---|---|

| 71M6532F-IGTR/F | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 71M6534-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 71M6531D-IMR/F | 功能描述:计量片上系统 - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531D-IMR/F1 | 功能描述:计量片上系统 - SoC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531D-IMR/F2 | 功能描述:计量片上系统 - SoC Residential Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 处理器系列:71M6511 类型:Metering SoC 最大时钟频率:70 Hz 程序存储器大小:64 KB 数据 RAM 大小:7 KB 接口类型:UART 可编程输入/输出端数量:12 片上 ADC: 安装风格:SMD/SMT 封装 / 箱体:LQFP-64 封装:Reel |

| 71M6531F | 制造商:TERIDIAN 制造商全称:TERIDIAN 功能描述:Energy Meter IC |

| 71M6531F-DB | 功能描述:开发板和工具包 - 8051 71M6531F Demo Brd RoHS:否 制造商:Silicon Labs 产品:Development Kits 工具用于评估:C8051F960, Si7005 核心: 接口类型:USB 工作电源电压: |

发布紧急采购,3分钟左右您将得到回复。