- 您现在的位置:买卖IC网 > PDF目录68816 > 7805ALPRPDB (MAXWELL TECHNOLOGIES) 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDIP28 PDF资料下载

参数资料

| 型号: | 7805ALPRPDB |

| 厂商: | MAXWELL TECHNOLOGIES |

| 元件分类: | ADC |

| 英文描述: | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDIP28 |

| 封装: | RAD-PAK, DIP-28 |

| 文件页数: | 6/34页 |

| 文件大小: | 605K |

| 代理商: | 7805ALPRPDB |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页

Memory

PRELIMINARY

14

All data sheets are subject to change without notice

2001 Maxwell Technologies

All rights reserved.

16-Bit Latchup Protected ADC

7805ALP

12.19.01 Rev 6

1000583

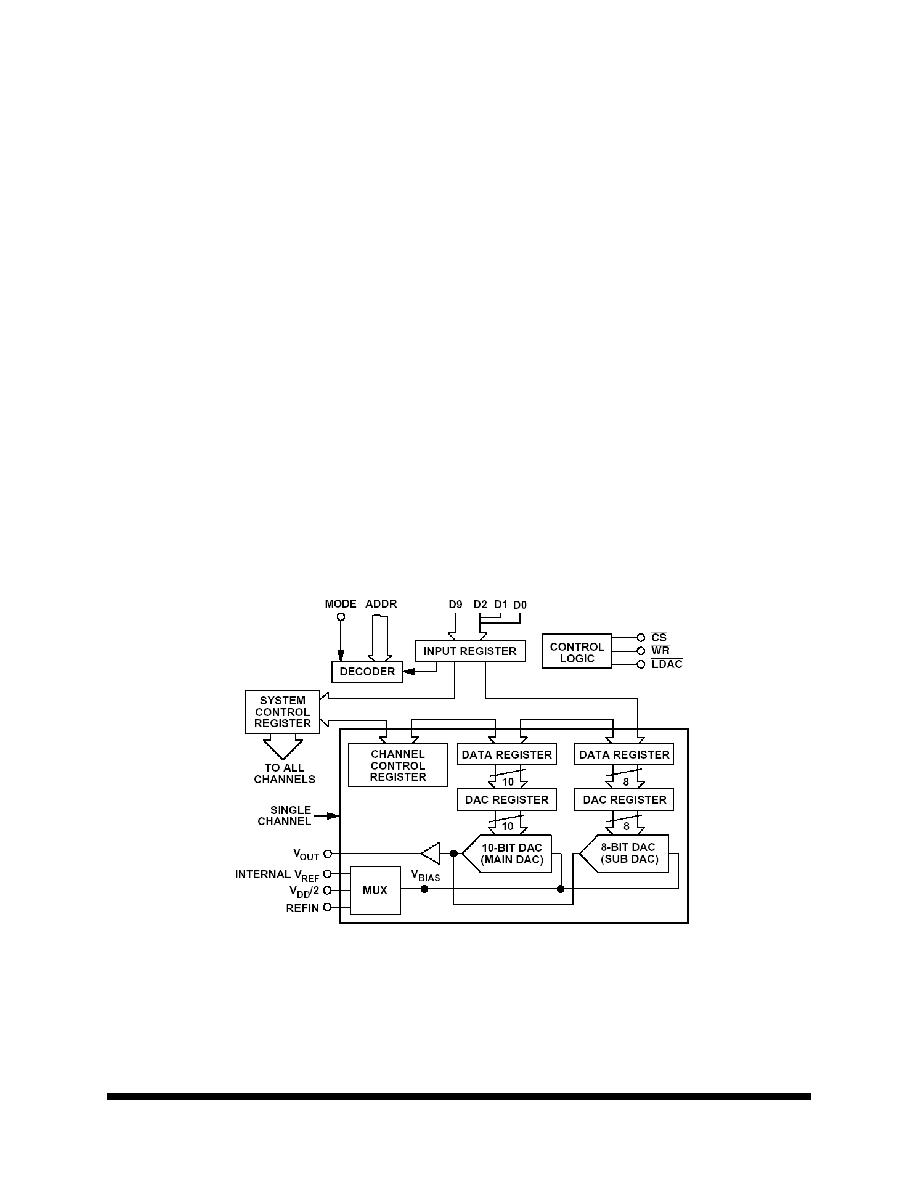

AD7805/AD7809 INTERFACE SECTION

The 7805 is a parallel data input device and contains both control registers and data registers. The system control reg-

ister has global control over all DACs in the package while the channel control register allows control over individual

DACs in the package. Two data registers are also available, one for the 10-bit Main DAC and the second for the 8-bit

Sub DAC. In the parallel mode, CS and WR, in association with the address pins, control the loading of data. Data is

transferred from the data register to the DAC register under the control of the LDAC signal. Only data contained in the

DAC register determines the analog output of any DAC. The timing diagram for 10-bit parallel loading is shown in Fig-

ure 2. The MODE pin on the device determines whether writing is to the data registers or to the control registers.

When MODE is at a logic one, writing is to the data registers. In the next write to the data registers a bit in the channel

control register determines whether the Main DAC or the Sub DAC is addressed. This means that to address either

the Main or the Sub DAC the Main/Sub bit in the control register has to be set appropriately before the data register

write. A logic zero on the mode pin enables writing to the control register. Bit MD0 determines whether writing is to the

system control register or to the addressed channel control register.

Bringing the CLR line low resets the DAC registers to one of two known conditions depending on the coding scheme

selected. The hardware clear affects both the Main and Sub DAC registers. With offset binary coding a clear sets the

output of the Main DAC to the bottom of the transfer function, VBIAS/16. With twos complement coding the output of

the DAC is cleared to midscale which is VBIAS. A hardware clear always clears the output of the Sub DAC to midscale

thus the output of the Sub DAC makes zero contribution to the output of the channel.

FIGURE 10. 7805ALP INTERNAL REGISTERS

相关PDF资料 |

PDF描述 |

|---|---|

| 7805ALPRPFS | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, DFP28 |

| 7805ALPRPDS | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDIP28 |

| 7805ALPRPFB | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, DFP28 |

| 7846RPFE | PARALLEL, WORD INPUT LOADING, 16-BIT DAC, DFP28 |

| 7846RPFB | PARALLEL, WORD INPUT LOADING, 16-BIT DAC, DFP28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| 7805ALPRPDE | 制造商:MAXWELL 制造商全称:Maxwell Technologies 功能描述:16-Bit Latchup Protected ADC |

| 7805ALPRPDH | 制造商:MAXWELL 制造商全称:Maxwell Technologies 功能描述:16-Bit Latchup Protected ADC |

| 7805ALPRPDI | 制造商:MAXWELL 制造商全称:Maxwell Technologies 功能描述:16-Bit Latchup Protected ADC |

| 7805ALPRPDK | 制造商:MAXWELL 制造商全称:Maxwell Technologies 功能描述:16-Bit Latchup Protected ADC |

| 7805ALPRPFE | 制造商:MAXWELL 制造商全称:Maxwell Technologies 功能描述:16-Bit Latchup Protected ADC |

发布紧急采购,3分钟左右您将得到回复。