参数资料

| 型号: | ACS8946T |

| 厂商: | Semtech |

| 文件页数: | 37/40页 |

| 文件大小: | 0K |

| 描述: | IC JITTER ATT MULT PLL 48-QFN |

| 标准包装: | 1 |

| 类型: | 时钟/频率发生器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH |

| 输入: | LVPECL |

| 输出: | CML,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:4 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 625MHz |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-VFQFN 裸露焊盘 |

| 供应商设备封装: | 48-QFN(7x7) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页

ADVANCED COMMUNICATIONS

FINAL

DATASHEET

Revision 3/November 2006 Semtech Corp.

Page 6

www.semtech.com

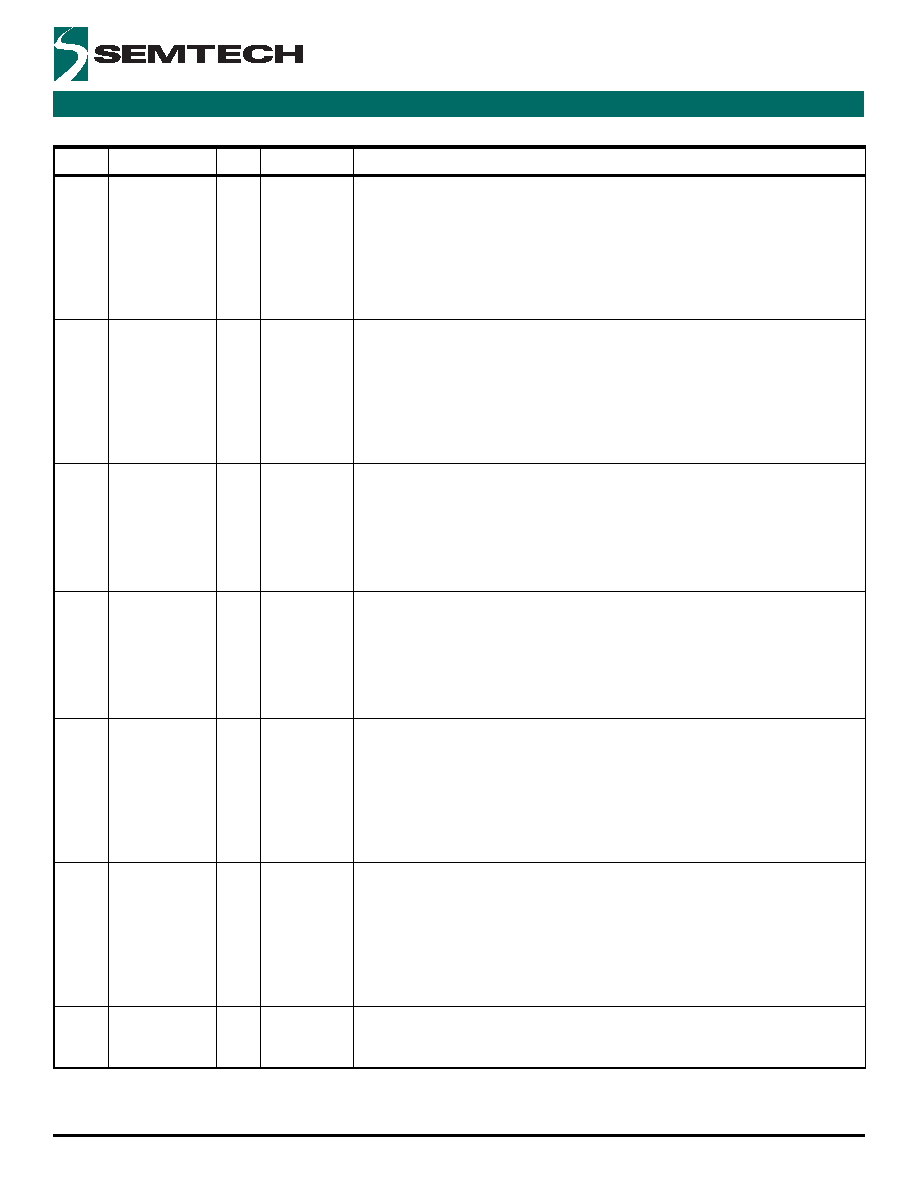

ACS8946 JAM PLL

24

CFG_IN6

I

LVTTL/

LVCMOSD

Configuration pin for setting up the device just after power-up or after a system reset (via

pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just

after power-up, so that the device works out whether this pin is connected to ground,

power or one of the configuration outputs at pins 13 to 16. This pin is used with pin 25 to

to set the value of the odd divider, which applies a division of 1/3/5/7/9/11/13 or 15 to

the otherwise selected spot frequency, on each of the four outputs OUTN/P[4:1]. It is also

used to enable or disable the lock detector (pin 17 LOCKB), and to set the output pad

mode (CML or PECL) for OUT3 and OUT4 as shown in Table 13.

25

CFG_IN7

I

LVTTL/

LVCMOSD

Configuration pin for setting up the device just after power-up or after a system reset (via

pin 40, RESETB). This configuration pin is analyzed during the configuration phase, just

after power-up, so that the device works out whether this pin is connected to ground,

power or one of the configuration outputs at pins 13 to 16. This pin is used with pin 24 to

to set the value of the odd divider, which applies a division of 1/3/5/7/9/11/13 or 15 to

the otherwise selected spot frequency on each of the four outputs OUTN/P[4:1]. It is also

used to enable or disable the lock detector (pin 17 LOCKB) and to set the output pad

mode (CML or PECL) for OUT3 and OUT4 as shown in Table 13.

27

CLK1N

I

LVPECL

Input reference clock that the PLL will phase and frequency lock to. Can accept

19.44 MHz, 38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz, and

frequencies near to these so long as the chosen frequency remains stable to within the

tracking range of ±400 ppm. (See “Inputs” on page 8 and Table 10). Can accept LVPECL

or LVDS or CML inputs given suitable external interface components. Partnered with pin

28. This clock or CLK2 can be automatically or manually selected as the reference clock,

see Table 4.

28

CLK1P

I

LVPECL

Input reference clock that the PLL will phase and frequency lock to. Can accept

19.44 MHz, 38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz and

frequencies near to these so long as the chosen frequency remains stable to within the

tracking range of ±400 ppm. (See “Inputs” on page 8 and Table 10). Can accept LVPECL

or LVDS or CML inputs given suitable external interface components. Partnered with pin

27. This clock or CLK2 can be automatically or manually selected as the reference clock,

see Table 4.

30

CLK2N

I

LVPECL

Second Input reference clock that the PLL will phase and frequency lock to. Input

reference clock that the PLL will phase and frequency lock to. Can accept 19.44 MHz,

38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz, and frequencies

near to these so long as the chosen frequency remains stable to within the tracking

range of ±400 ppm. (See “Inputs” on page 8 and Table 10). Can accept LVPECL or LVDS

or CML inputs given suitable external interface components. Partnered with pin 31. This

clock or CLK1 can be automatically or manually selected as the reference clock, see

31

CLK2P

I

LVPECL

Second Input reference clock that the PLL will phase and frequency lock to. Input

reference clock that the PLL will phase and frequency lock to. Can accept 19.44 MHz,

38.88 MHz, 77.76 MHz, 125.00 MHz, 155.52 MHz or 156.25 MHz, and frequencies

near to these so long as the chosen frequency remains stable to within the tracking

range of ±400 ppm. (See “Inputs” on page 8 and Table 10). Can accept LVPECL or LVDS

or CML inputs given suitable external interface components. Partnered with pin 30. This

clock or CLK2 can be automatically or manually selected as the reference clock, see

32

SEL_CLK2

I

LVTTL/

LVCMOSD

Used in combination with pin 33, AUTO_SEL, either to select the CLK2 clock (high) or

CLK1 clock (low) in manual control mode, or to select automatic switching mode, as

described in Table 4.

Table 3 Functional Pins (cont...)

Pin No.

Symbol

I/O

Type

Description

相关PDF资料 |

PDF描述 |

|---|---|

| ACS8947T | IC JITTER ATT MULT PLL 48-QFN |

| AD10200BZ | IC ADC DUAL 12BIT 68-CLCC |

| AD10242BZ | IC ADC DUAL 12BIT 68-CLCC |

| AD10465BZ | IC ADC DUAL 14BIT 68-CLCC |

| AD13280AZ | IC ADC 12BIT 68CLCC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ACS8947T | 功能描述:IC JITTER ATT MULT PLL 48-QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| ACS9010 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Optoelectronic |

| ACS9510/50EVB | 制造商:Semtech Corporation 功能描述: |

| ACS9510EVB | 功能描述:EVALUATION BOARD FOR ACS9510 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:ToPSync™ 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| ACS9510T | 制造商:Semtech Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。