参数资料

| 型号: | AD5422BREZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 22/44页 |

| 文件大小: | 0K |

| 描述: | IC DAC 16BIT 1CH 24TSSOP |

| 产品培训模块: | Power Line Monitoring Data Converter Fundamentals DAC Architectures |

| 设计资源: | 16-Bit Fully Isolated Output Module Using AD5422 and ADuM1401 (CN0065) Simplified 16-Bit Voltage Output and 4 mA-to-20 mA Output Solution Using AD5422 (CN0077) |

| 标准包装: | 62 |

| 设置时间: | 25µs |

| 位数: | 16 |

| 数据接口: | MICROWIRE?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字,双 ± |

| 功率耗散(最大): | 950mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm)裸露焊盘 |

| 供应商设备封装: | 24-TSSOP 裸露焊盘 |

| 包装: | 管件 |

| 输出数目和类型: | 1 电流,单极;1 电流,双极;1 电压,单极;1 电压,双极 |

| 采样率(每秒): | 40k |

| 产品目录页面: | 782 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

Data Sheet

AD5412/AD5422

Rev. I | Page 29 of 44

Readback Operation

Readback mode is invoked by setting the address byte and

read address when writing to the input register (see Table 9 and

NOP command, which clocks out the data from the previously

addressed register as shown in Figure 3.

By default the SDO pin is disabled after having addressed the

enables the SDO pin in anticipation of data being clocked out.

After the data has been clocked out on SDO, a rising edge on

LATCH disables (tristate) the SDO pin. To read back the data

register, for example, implement the following sequence:

1. Write 0x020001 to the input register. This configures the

part for read mode with the data register selected.

2. Follow this with a second write: a NOP condition, which is

0x000000. During this write, the data from the register is

clocked out on the SDO line.

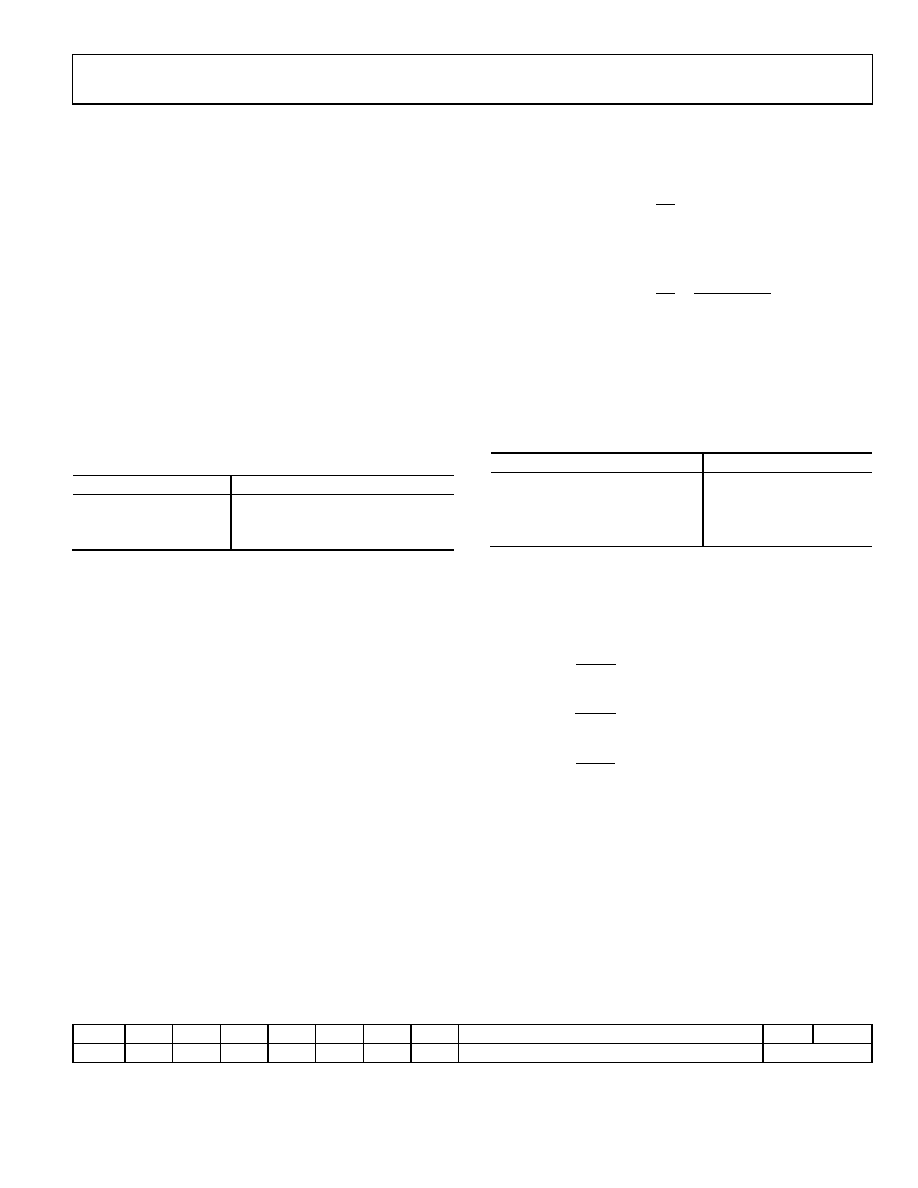

Table 9. Read Address Decoding

Read Address

Function

00

Read status register

01

Read data register

10

Read control register

POWER-ON STATE

circuit ensures that all registers are loaded with zero-code. As

such, both outputs are disabled; that is, the VOUT and IOUT pins

are in tristate. The +VSENSE pin is internally connected to ground

through a 40 kΩ resistor. Therefore, if the VOUT and +VSENSE pins

are connected together, VOUT is effectively clamped to ground

through a 40 kΩ resistor. Also upon power-on, internal

calibration registers are read, and the data is applied to internal

calibration circuitry. For a reliable read operation, there must be

sufficient voltage on the AVDD supply when the read event is

triggered by the DVCC power supply powering up. Powering up

the DVCC supply after the AVDD supply ensures this. If DVCC and

AVDD are powered up simultaneously or the internal DVCC is

enabled, the supplies should be powered up at a rate greater

than, typically, 500 V/sec or 24 V/50 ms. If this cannot be

achieved, issue a reset command to the AD5412/AD5422 after

power-on; this performs a power-on-reset event, reading the

calibration registers and ensures specified operation of the

internal reference to settle to its correct trim value, 40 s should

be allowed after a successful power on reset.

Voltage Output

For a unipolar voltage output range, the output voltage can be

expressed as

×

=

N

REFIN

OUT

D

Gain

V

2

For a bipolar voltage output range, the output voltage can be

expressed as

2

REFIN

N

REFIN

OUT

V

Gain

D

Gain

V

×

×

=

where:

D is the decimal equivalent of the code loaded to the DAC.

N is the bit resolution of the DAC.

VREFIN is the reference voltage applied at the REFIN pin.

Gain is an internal gain whose value depends on the output

range selected by the user as shown in Table 10.

Table 10. Internal Gain Value

Output Range

Gain Value

+5 V

1

+10 V

2

±5 V

2

±10 V

4

Current Output

For the 0 mA to 20 mA, 0 mA to 24 mA, and 4 mA to 20 mA

current output ranges, the output current is respectively

expressed as

D

I

N

OUT

×

=

2

mA

20

D

I

N

OUT

×

=

2

mA

24

mA

4

2

mA

16

+

×

=

D

I

N

OUT

where:

D is the decimal equivalent of the code loaded to the DAC.

N is the bit resolution of the DAC.

Table 11. Input Shift Register Contents for a Read Operation

MSB

LSB

D23

D22

D21

D20

D19

D18

D17

D16

D15 to D2

D1

D0

0

1

0

Read address

1

X = don’t care.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-BTT-MY-F4 | CONVERTER MOD DC/DC 6.5V 50W |

| VE-J4D-MZ-F2 | CONVERTER MOD DC/DC 85V 25W |

| VE-B4Z-MU-F1 | CONVERTER MOD DC/DC 2V 80W |

| VI-BTT-MY-F3 | CONVERTER MOD DC/DC 6.5V 50W |

| LTC1454IS#PBF | IC D/A CONV 12BIT R-R DUAL16SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5422BREZ-REEL | 功能描述:IC DAC 16BIT 1CH SRL INP 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD5424 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual 8-,10-,12-Bit High Bandwidth Multiplying DACs with Serial Interface |

| AD5424_1 | 制造商:AD 制造商全称:Analog Devices 功能描述:8-/10-/12-Bit, High Bandwidth Multiplying DACs with Parallel Interface |

| AD5424BRU | 制造商:Analog Devices 功能描述:DAC SGL R-2R 8BIT 16TSSOP - Bulk |

| AD5424YCP | 制造商:Analog Devices 功能描述:DAC 1-CH R-2R 8-bit 20-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:8-BIT IOUT DAC PARELLED INT/FACE I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。