参数资料

| 型号: | AD5422BREZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/44页 |

| 文件大小: | 0K |

| 描述: | IC DAC 16BIT 1CH 24TSSOP |

| 产品培训模块: | Power Line Monitoring Data Converter Fundamentals DAC Architectures |

| 设计资源: | 16-Bit Fully Isolated Output Module Using AD5422 and ADuM1401 (CN0065) Simplified 16-Bit Voltage Output and 4 mA-to-20 mA Output Solution Using AD5422 (CN0077) |

| 标准包装: | 62 |

| 设置时间: | 25µs |

| 位数: | 16 |

| 数据接口: | MICROWIRE?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字,双 ± |

| 功率耗散(最大): | 950mW |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm)裸露焊盘 |

| 供应商设备封装: | 24-TSSOP 裸露焊盘 |

| 包装: | 管件 |

| 输出数目和类型: | 1 电流,单极;1 电流,双极;1 电压,单极;1 电压,双极 |

| 采样率(每秒): | 40k |

| 产品目录页面: | 782 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

Data Sheet

AD5412/AD5422

Rev. I | Page 35 of 44

Table 23. Slew Rate Update Clock Options

SR Clock

Update Clock Frequency (Hz)

0000

257,730

0001

198,410

0010

152,440

0011

131,580

0100

115,740

0101

69,440

0110

37,590

0111

25,770

1000

20,160

1001

16,030

1010

10,290

1011

8280

1100

6900

1101

5530

1110

4240

1111

3300

The time it takes for the output to slew over a given output

range can be expressed as follows:

Size

LSB

Frequency

Clock

Update

Size

Step

Change

Output

Time

Slew

×

=

(1)

where:

Slew Time is expressed in seconds.

Output Change is expressed in amps for IOUT or volts for VOUT.

When the slew rate control feature is enabled, all output

changes change at the programmed slew rate; if the CLEAR

pin is asserted, the output slews to the zero-scale value at the

programmed slew rate. The output can be halted at its current

value with a write to the control register. To avoid halting the

output slew, the slew active bit (see Table 19) can be read to

check that the slew has completed before writing to any of the

given value is the same for all output ranges. The step size,

however, varies across output ranges for a given value of step

size because the LSB size is different for each output range.

Table 24 shows the range of programmable slew times for a full-

scale change on any of the output ranges. The values in Table 24

were obtained using Equation 1.

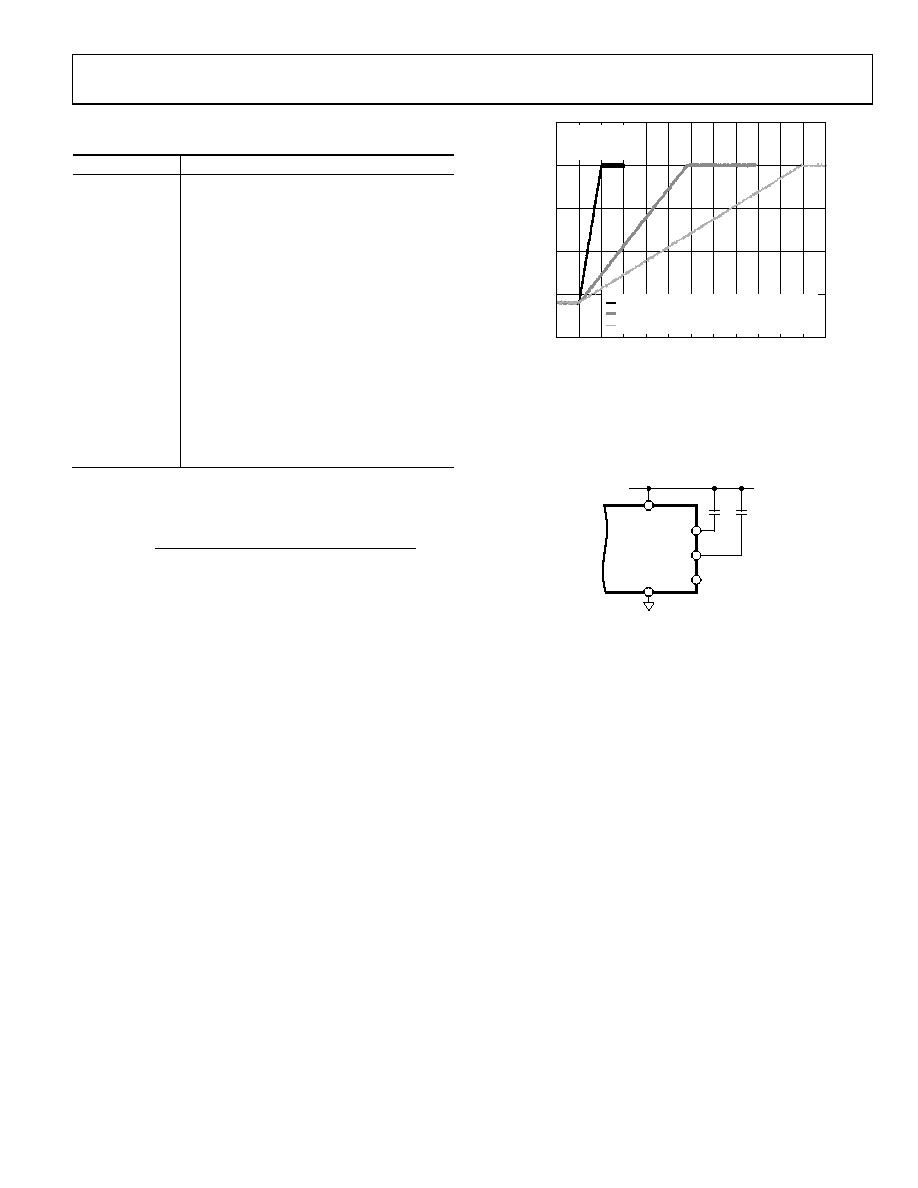

The digital slew rate control feature results in a staircase

formation on the current output, as shown in Figure 76. This

figure also shows how the staircase can be removed by

connecting capacitors to the CAP1 and CAP2 pins, as described

0

5

10

15

20

25

–10

0

10

20

30

40

50

60

70

80

90

100 110

O

UT

P

UT

CURRE

NT

(

mA)

TIME (ms)

TA = 25°C

AVDD = 24V

RLOAD = 300

06996-

139

10ms RAMP, SR CLOCK = 0x1, SR STEP = 0x5

50ms RAMP, SR CLOCK = 0xA, SR STEP = 0x7

100ms RAMP, SR CLOCK = 0x8, SR STEP = 0x5

Figure 72. Output Current Slewing Under Control of the Digital Slew Rate

Control Feature

IOUT FILTERING CAPACITORS (LFCSP PACKAGE)

Capacitors can be placed between CAP1 and AVDD, and CAP2

CAP1

AVDD

C1

C2

AVDD

AD5412/

AD5422 CAP2

GND

06996-

062

IOUT

Figure 73. IOUT Filtering Capacitors

The CAP1 and CAP2 pins are available only on the LFCSP

package. The capacitors form a filter on the current output

circuitry, as shown in Figure 74, reducing the bandwidth and

the slew rate of the output current. Figure 75 shows the effect

the capacitors have on the slew rate of the output current. To

achieve significant reductions in the rate of change, very large

capacitor values are required, which may not be suitable in

some applications. In this case, the digital slew rate control

feature can be used. The capacitors can be used in conjunction

with the digital slew rate control feature as a means of

smoothing out the steps caused by the digital code increments,

as shown in Figure 76.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-BTT-MY-F4 | CONVERTER MOD DC/DC 6.5V 50W |

| VE-J4D-MZ-F2 | CONVERTER MOD DC/DC 85V 25W |

| VE-B4Z-MU-F1 | CONVERTER MOD DC/DC 2V 80W |

| VI-BTT-MY-F3 | CONVERTER MOD DC/DC 6.5V 50W |

| LTC1454IS#PBF | IC D/A CONV 12BIT R-R DUAL16SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD5422BREZ-REEL | 功能描述:IC DAC 16BIT 1CH SRL INP 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数模转换器 系列:- 标准包装:47 系列:- 设置时间:2µs 位数:14 数据接口:并联 转换器数目:1 电压电源:单电源 功率耗散(最大):55µW 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:管件 输出数目和类型:1 电流,单极;1 电流,双极 采样率(每秒):* |

| AD5424 | 制造商:AD 制造商全称:Analog Devices 功能描述:Dual 8-,10-,12-Bit High Bandwidth Multiplying DACs with Serial Interface |

| AD5424_1 | 制造商:AD 制造商全称:Analog Devices 功能描述:8-/10-/12-Bit, High Bandwidth Multiplying DACs with Parallel Interface |

| AD5424BRU | 制造商:Analog Devices 功能描述:DAC SGL R-2R 8BIT 16TSSOP - Bulk |

| AD5424YCP | 制造商:Analog Devices 功能描述:DAC 1-CH R-2R 8-bit 20-Pin LFCSP EP 制造商:Rochester Electronics LLC 功能描述:8-BIT IOUT DAC PARELLED INT/FACE I.C. - Bulk |

发布紧急采购,3分钟左右您将得到回复。