- 您现在的位置:买卖IC网 > PDF目录373890 > AD6624A (Analog Devices, Inc.) Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) PDF资料下载

参数资料

| 型号: | AD6624A |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| 中文描述: | 四通道,100 MSPS的数字接收信号处理器(RSP) |

| 文件页数: | 19/40页 |

| 文件大小: | 636K |

| 代理商: | AD6624A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD6624A

–19–

where

input_level

is the largest fraction of full-scale possible at

the input to the AD6624A (normally 1). The rCIC2 scale factor

is always used whether or not the rCIC2 is bypassed.

Moreover, there are two scale registers (rCIC2_LOUD[4:0]

Bits 4

–

0 in x92), and (rCIC2_QUIET[4:0] Bits 9

–

5 in 0x92)

that are used in conjunction with the computed S

rCIC2

which

determines the overall rCIC2 scaling. The S

rCIC2

value must

be summed with the values in each respective scale register and

ExpOff, to determine the scale value that must be placed in the

rCIC2 scale register. This number must be less than 32 or the

interpolation and decimation rates must be adjusted to validate

this equation. The ceil function denotes the next whole integer

and the floor function denotes the previous whole integer. For

example, the ceil(4.5) is 5 while the floor(4.5) is 4.

The gain and passband droop of the rCIC2 should be calculated

by the equations above, as well as the filter transfer equations that

follow. Excessive passband droop can be compensated for in the

RCF stage by peaking the passband by the inverse of the roll-off.

scaled input

scaled input

_

IN

IN

ExpInv

ExpInv

,

Exp

rCIC

Exp

rCIC

_

,

mod(

, )

2 8

mod(

, )

2 8

=

=

×

×

=

=

+

+

2

2

0

1

7

(7)

where:

IN

is the value of IN[15:0],

Exp

is the value of EXP[2:0],

and

rCIC

2 is the value of the 0x92 (rCIC2_QUIET[4:0] and

rCIC2_LOUD[4:0]) scale register.

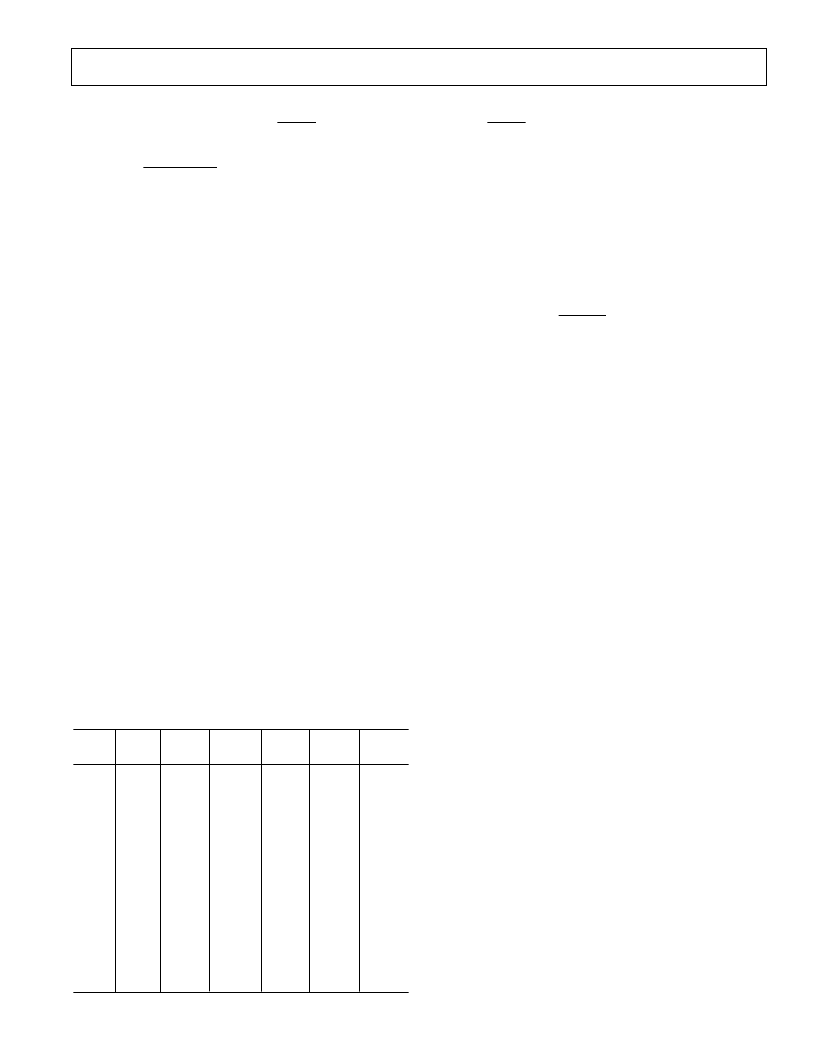

rCIC2 Rejection

Table III illustrates the amount of bandwidth in percent of the

data rate into the rCIC2 stage. The data in this table may be

scaled to any other allowable sample rate up to 80 MHz in

Single Channel Mode or 40 MHz in Diversity Channel Mode.

The table can be used as a tool to decide how to distribute the

decimation between rCIC2, CIC5, and the RCF.

Table III. SSB rCIC2 Alias Rejection Table (f

SAMP

= 1)

Bandwidth Shown in Percentage of f

SAMP

M

CIC5

/

L

rCIC2

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

–50 dB –60 dB

–70 dB

–80 dB –90 dB

–100 dB

1.79

1.508

1.217

1.006

0.853

0.739

0.651

0.581

0.525

0.478

0.439

0.406

0.378

0.353

0.331

1.007

0.858

0.696

0.577

0.49

0.425

0.374

0.334

0.302

0.275

0.253

0.234

0.217

0.203

0.19

0.566

0.486

0.395

0.328

0.279

0.242

0.213

0.19

0.172

0.157

0.144

0.133

0.124

0.116

0.109

0.318

0.274

0.223

0.186

0.158

0.137

0.121

0.108

0.097

0.089

0.082

0.075

0.07

0.066

0.061

0.179

0.155

0.126

0.105

0.089

0.077

0.068

0.061

0.055

0.05

0.046

0.043

0.04

0.037

0.035

0.101

0.087

0.071

0.059

0.05

0.044

0.038

0.034

0.031

0.028

0.026

0.024

0.022

0.021

0.02

Example Calculations

Goal: Implement a filter with an Input Sample Rate of 10 MHz

requiring 100 dB of alias rejection for a

±

7 kHz passband.

Solution: First determine the percentage of the sample rate that

is represented by the passband.

BW

kHz

MHz

FRACTION

=

×

=

100

7

10

0 07

.

(8)

Find the

–

100 dB column in Table III and look down this column

for a value greater than or equal to your passband percentage of

the clock rate. Then look across to the extreme left column and

find the corresponding rate-change factor (M

rCIC2

/L

rCIC2

). Refer-

ring to the table, notice that for a M

rCIC2

/L

rCIC2

of 4, the frequency

having

–

100 dB of alias rejection is 0.071 percent, which is

slightly greater than the 0.07 percent calculated. Therefore, for

this example, the maximum bound on rCIC2 rate change is 4.

A higher chosen M

rCIC2

/L

rCIC2

means less alias rejection than

the 100 dB required.

An M

rCIC2

/L

rCIC2

of less than four would still yield the required

rejection; however, the power consumption can be minimized

by decimating as much as possible in this rCIC2 stage. Decima-

tion in rCIC2 lowers the data rate, and thus reduces power

consumed in subsequent stages. It should also be noted that

there is more than one way to determine the decimation by 4. A

decimation of 4 is the same as an L/M ratio of 0.25. Thus any

integer combination of L/M that yields 0.25 will work (1/4, 2/8,

or 4/16). However, for the best dynamic range, the simplest

ratio should be used. For example, 1/4 gives better performance

than 4/16.

Decimation and Interpolation Registers

rCIC2 decimation values are stored in register 0x90. This is a

12-bit register and contains the decimation portion less 1. The

interpolation portion is stored in register 0x91. This 9-bit value

holds the interpolation less one.

rCIC2 Scale

Register 0x92 contains the scaling information for this section of

the circuit. The primary function is to store the scale value

computed in the sections above.

Bits 4

–

0 (rCIC2_LOUD[4:0]) of this register are used to con-

tain the scaling factor for the rCIC2 during conditions of strong

signals. These five bits represent the rCIC2 scalar calculated above

plus any external signal scaling with an attenuator.

Bits 9

–

5 (rCIC2_QUIET[4:0]) of this register are used to con-

tain the scaling factor for the rCIC2 during conditions of weak

signals. In this register, no external attenuator would be used

and is not included. Only the value computed above is stored in

these bits.

Bit 10 of this register is used to indicate the value of the external

exponent. If this bit is set LOW, each external exponent repre-

sents 6 dB per step as in the AD6600. If this bit is set to HIGH,

each exponent represents a 12 dB step.

S

ceil

M

floor

M

L

M

L

floor

M

L

OL

M

L

input level

_

rCIC

rCIC

rCIC

rCIC

rCIC

rCIC

rCIC

rCIC

CIC

rCIC

×

rCIC

S

rCIC

2

2

2

2

2

2

2

2

2

2

2

2

2

2

1

2

2

=

+

×

×

×

+

(

=

×

log

)

(6)

相关PDF资料 |

PDF描述 |

|---|---|

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6630AR-REEL | Differential, Low Noise IF Gain Block with Output Clamping |

| AD6630AR | Differential, Low Noise IF Gain Block with Output Clamping |

| AD6630PCB | Differential, Low Noise IF Gain Block with Output Clamping |

| AD6630R | Differential, Low Noise IF Gain Block with Output Clamping |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6624AABC | 制造商:Advanced Micro Devices 功能描述: |

| AD6624AABCZ | 功能描述:DIGITAL SIGNAL PROC 196 CSP-BGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| AD6624AS | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AS/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624S/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

发布紧急采购,3分钟左右您将得到回复。