- 您现在的位置:买卖IC网 > PDF目录373890 > AD6624A (Analog Devices, Inc.) Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) PDF资料下载

参数资料

| 型号: | AD6624A |

| 厂商: | Analog Devices, Inc. |

| 英文描述: | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| 中文描述: | 四通道,100 MSPS的数字接收信号处理器(RSP) |

| 文件页数: | 5/40页 |

| 文件大小: | 636K |

| 代理商: | AD6624A |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页

REV. 0

AD6624A

–5–

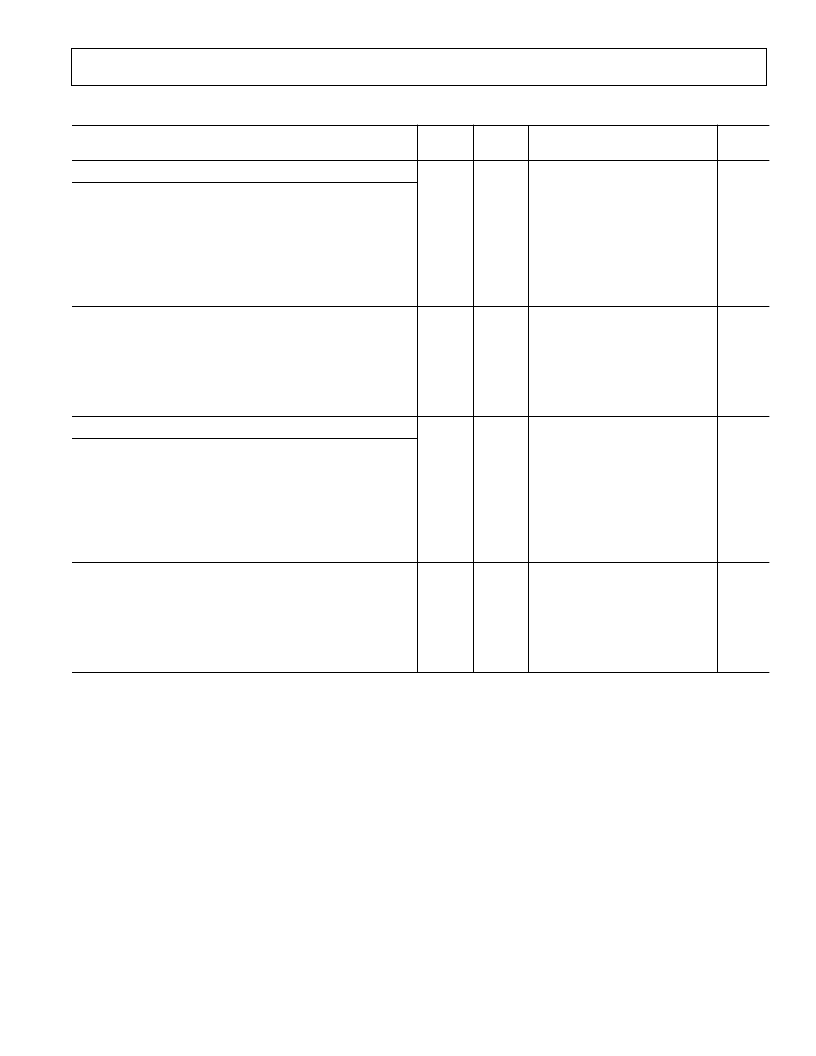

MICROPROCESSOR PORT TIMING CHARACTERISTICS

1, 2

Test

Level

AD6624AS

Typ

Parameter (Conditions)

Temp

Min

Max

Unit

MICROPROCESSOR PORT, MODE INM (MODE = 0)

MODE INM Write Timing

:

t

SC

t

HC

t

HWR

t

SAM

t

HAM

t

DRDY

t

ACC

MODE INM Read Timing

:

t

SC

t

HC

t

SAM

t

HAM

t

DRDY

t

ACC

MICROPROCESSOR PORT, MODE MNM (MODE = 1)

Control

3

to

↑

CLK Setup Time

Control

3

to

↑

CLK Hold Time

WR(

RW

)

to RDY(

DTACK

) Hold Time

Address/Data to

WR

(RW) Setup Time

Address/Data to RDY(

DTACK

) Hold Time

WR

(RW) to RDY(

DTACK

) Delay

WR

(RW) to RDY(

DTACK

) High Delay

Full

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

IV

5.5

1.0

8.0

–0.5

7.0

4.0

4

×

t

CLK

ns

ns

ns

ns

ns

ns

ns

5

×

t

CLK

9

×

t

CLK

Control

3

to

↑

CLK Setup Time

Control

3

to

↑

CLK Hold Time

Address to

RD

(

DS

) Setup Time

Address to Data Hold Time

RD

(

DS

) to RDY(

DTACK

) Delay

RD

(

DS

) to RDY(

DTACK

) High Delay

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

4.0

2.0

0.0

7.0

4.0

8

×

t

CLK

ns

ns

ns

ns

ns

ns

10

×

t

CLK

13

×

t

CLK

MODE MNM Write Timing

:

t

SC

t

HC

t

HDS

t

HRW

t

SAM

t

HAM

t

ACC

MODE MNM Read Timing

:

t

SC

t

HC

t

SAM

t

HAM

t

ZD

t

ACC

Control

3

to

↑

CLK Setup Time

Control

3

to

↑

CLK Hold Time

DS

(

RD

) to

DTACK

(RDY) Hold Time

RW(

WR

) to

DTACK

(RDY) Hold Time

Address/Data to RW(

WR

) Setup Time

Address/Data to RW(

WR

) Hold Time

RW(

WR

) to

DTACK

(RDY) Low Delay

Full

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

IV

5.5

1.0

8.0

8.0

–0.5

7.0

4

×

t

CLK

ns

ns

ns

ns

ns

ns

ns

5

×

t

CLK

9

×

t

CLK

Control

3

to

↑

CLK Setup Time

Control

3

to

↑

CLK Hold Time

Address to

DS

(

RD

) Setup Time

Address to Data Hold Time

Data Three-State Delay

DS

(

RD

) to

DTACK

(RDY) Low Delay

Full

Full

Full

Full

Full

Full

IV

IV

IV

IV

IV

IV

4.0

2.0

0.0

7.0

7.0

8

×

t

CLK

ns

ns

ns

ns

ns

ns

10

×

t

CLK

13

×

t

CLK

NOTES

1

All Timing Specifications valid over VDD range of 2.375 V to 2.675 V and VDDIO range of 3.0 V to 3.6 V.

2

C

= 40 pF on all outputs unless otherwise specified.

3

Specification pertains to control signals: RW, (

WR

),

DS

, (

RD

),

CS

.

Specifications subject to change without notice.

相关PDF资料 |

PDF描述 |

|---|---|

| AD6624AABC | Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6630AR-REEL | Differential, Low Noise IF Gain Block with Output Clamping |

| AD6630AR | Differential, Low Noise IF Gain Block with Output Clamping |

| AD6630PCB | Differential, Low Noise IF Gain Block with Output Clamping |

| AD6630R | Differential, Low Noise IF Gain Block with Output Clamping |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD6624AABC | 制造商:Advanced Micro Devices 功能描述: |

| AD6624AABCZ | 功能描述:DIGITAL SIGNAL PROC 196 CSP-BGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| AD6624AS | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

| AD6624AS/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 100 MSPS Digital Receive Signal Processor (RSP) |

| AD6624S/PCB | 制造商:AD 制造商全称:Analog Devices 功能描述:Four-Channel, 80 MSPS Digital Receive Signal Processor (RSP) |

发布紧急采购,3分钟左右您将得到回复。