- 您现在的位置:买卖IC网 > PDF目录1980 > AD7190BRUZ-REEL (Analog Devices Inc)IC ADC 2CH 24BIT W/PGA 24TSSOP PDF资料下载

参数资料

| 型号: | AD7190BRUZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/41页 |

| 文件大小: | 0K |

| 描述: | IC ADC 2CH 24BIT W/PGA 24TSSOP |

| 设计资源: | Precision Weigh Scale Design Using AD7190 with Internal PGA (CN0102) |

| 标准包装: | 2,500 |

| 位数: | 24 |

| 采样率(每秒): | 4.8k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 24-TSSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个差分,双极;4 个伪差分,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页

Data Sheet

AD7190

Rev. C | Page 33 of 40

CIRCUIT DESCRIPTION

ANALOG INPUT CHANNEL

The AD7190 has two differential/four pseudo differential analog

input channels which can be buffered or unbuffered. In buffered

mode (the BUF bit in the configuration register is set to 1), the

input channel feeds into a high impedance input stage of the

buffer amplifier. Therefore, the input can tolerate significant

source impedances and is tailored for direct connection to

external resistive-type sensors such as strain gauges or resistance

temperature detectors (RTDs).

When BUF = 0, the part is operated in unbuffered mode. This

results in a higher analog input current. Note that this unbuffered

input path provides a dynamic load to the driving source.

Therefore, resistor/capacitor combinations on the input pins

can cause gain errors, depending on the output impedance of

the source that is driving the ADC input. Table 22 shows the

allowable external resistance/capacitance values for unbuffered

mode at a gain of 1 such that no gain error at the 20-bit level is

introduced.

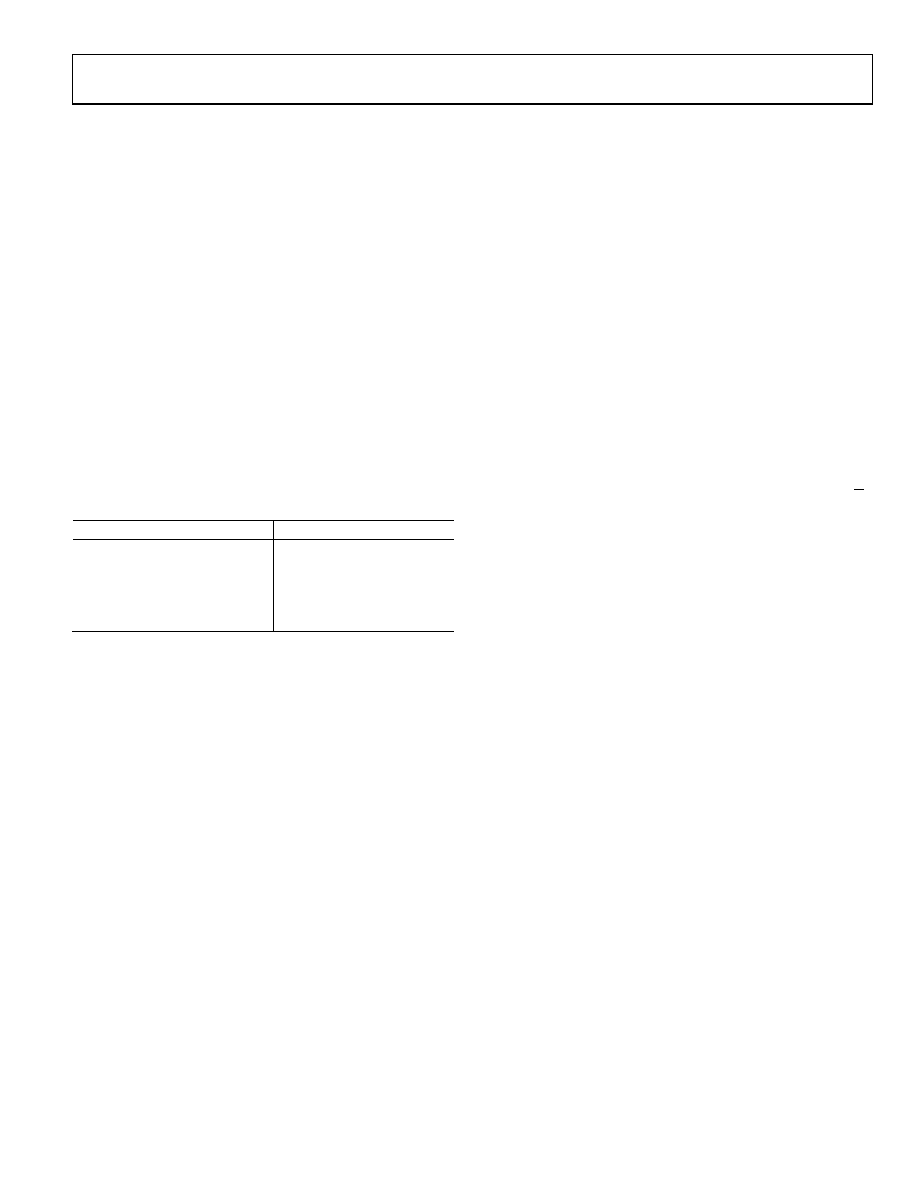

Table 22. External R-C Combination for No 20-Bit Gain Error

C (pF)

R ()

50

1.4 k

100

850

500

300

1000

230

5000

30

The absolute input voltage range in buffered mode is restricted

to a range between AGND + 250 mV and AVDD – 250 mV. Care

must be taken in setting up the common-mode voltage so that

these limits are not exceeded. Otherwise, there is degradation in

linearity and noise performance.

The absolute input voltage in unbuffered mode includes the

range between AGND – 50 mV and AVDD + 50 mV. The

negative absolute input voltage limit does allow the possibility

of monitoring small true bipolar signals with respect to AGND.

PGA

When the gain stage is enabled, the output from the buffer is

applied to the input of the programmable gain array (PGA).

The presence of the PGA means that signals of small amplitude

can be gained within the AD7190 while still maintaining excel-

lent noise performance. For example, when the gain is set to

128, the rms noise is 8.5 nV, typically, when the output data rate

is 4.7 Hz, which is equivalent to 23 bits of effective resolution or

20.5 bits of noise-free resolution.

The AD7190 can be programmed to have a gain of 1, 8, 16, 32,

64, and 128 using Bit G2 to Bit G0 in the configuration register.

Therefore, with an external 2.5 V reference, the unipolar ranges

are from 0 mV to 19.53 mV to 0 V to 2.5 V, and the bipolar

ranges are from ±19.53 mV to ±2.5 V.

The analog input range must be limited to (AVDD 1.25 V)/gain

because the PGA requires some headroom. Therefore, if AVDD =

5 V, the maximum analog input that can be applied to the

AD7190 is 0 to 3.75 V/gain in unipolar mode or ±3.75 V/ gain

in bipolar mode.

BIPOLAR/UNIPOLAR CONFIGURATION

The analog input to the AD7190 can accept either unipolar or

bipolar input voltage ranges. A bipolar input range does not

imply that the part can tolerate negative voltages with respect

to system AGND. In pseudo-differential mode, signals are

referenced to AINCOM while in differential mode, signals are

referenced to the negative input of the differential pair. For

example, if AINCOM is 2.5 V and the AD7190 AIN1 analog

input is configured for unipolar mode with a gain of 2, the input

voltage range on the AIN1 pin is 2.5 V to 3.75 V when a 2.5 V

reference is used. If AINCOM is 2.5 V and the AD7190 AIN1

analog input is configured for bipolar mode with a gain of 2, the

analog input range on AIN1 is 1.25 V to 3.75 V.

The bipolar/unipolar option is chosen by programming the U/B

bit in the configuration register.

DATA OUTPUT CODING

When the ADC is configured for unipolar operation, the output

code is natural (straight) binary with a zero differential input

voltage resulting in a code of 00...00, a midscale voltage resulting

in a code of 100...000, and a full-scale input voltage resulting in

a code of 111...111. The output code for any analog input voltage

can be represented as

Code = (2N × AIN × gain)/VREF

When the ADC is configured for bipolar operation, the output

code is offset binary with a negative full-scale voltage resulting

in a code of 000...000, a zero differential input voltage resulting

in a code of 100...000, and a positive full-scale input voltage

resulting in a code of 111...111. The output code for any analog

input voltage can be represented as

Code = 2N–1 × [(AIN × gain/VREF) + 1]

where:

AIN is the analog input voltage.

gain is the PGA setting (1 to 128).

N = 24.

CLOCK

The AD7190 includes an internal 4.92 MHz clock on-chip. This

internal clock has a tolerance of ±4%. Either the internal clock

or an external crystal/clock can be used as the clock source to

the AD7190. The clock source is selected using the CLK1 and

CLK0 bits in the mode register. When an external crystal is

used, it must be connected across the MCLK1 and MCLK2

pins. The crystal manufacturer recommends the load capaci-

tances required for the crystal. The MCLK1 and MCLK2 pins of

the AD7190 have a capacitance of 15 pF, typically. If an external

相关PDF资料 |

PDF描述 |

|---|---|

| AD7191BRUZ | IC ADC 2CH 24B SD 24TSSOP |

| AD7192BRUZ | IC ADC 24BIT 2CH W/PGA 24-TSSOP |

| AD7193BCPZ | IC ADC 24BIT SPI 4.8KHZ 32LFCSP |

| AD7194BCPZ | IC ADC 24BIT SPI 4.8K 32-LFCSP |

| AD7195BCPZ-RL7 | IC AFE 24BIT 4.8K 32LFSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD7190WBRUZ | 功能描述:24 Bit Analog to Digital Converter 2, 4 Input 1 Sigma-Delta 24-TSSOP 制造商:analog devices inc. 系列:- 包装:管件 零件状态:有效 位数:24 采样率(每秒):4.8k 输入数:2,4 输入类型:差分,个伪差分 数据接口:SPI,DSP 配置:MUX-PGA-ADC 无线电 - S/H:ADC:- A/D 转换器数:1 架构:三角积分 参考类型:外部, 内部 电压 - 电源,模拟:5V 电压 - 电源,数字:2.7 V ~ 5.25 V 特性:PGA,温度传感器 工作温度:-40°C ~ 105°C 封装/外壳:24-TSSOP(0.173",4.40mm 宽) 供应商器件封装:24-TSSOP 标准包装:1 |

| AD7190WBRUZ-RL | 制造商:Analog Devices 功能描述: |

| AD7191 | 制造商:AD 制造商全称:Analog Devices 功能描述:Pin-Programmable, Ultralow Noise, 24-Bit, Sigma-Delta ADC for Bridge Sensors |

| AD7191A/0B | 制造商:Sony Nec Optiarc America 功能描述:DOUBLE DUAL INTERNAL DVDRW PATA BEZEL 20X/18X12XRAM - Bulk |

| AD7191BRUZ | 功能描述:IC ADC 2CH 24B SD 24TSSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模数转换器 系列:- 标准包装:1,000 系列:- 位数:16 采样率(每秒):45k 数据接口:串行 转换器数目:2 功率耗散(最大):315mW 电压电源:模拟和数字 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) 输入数目和类型:2 个单端,单极 |

发布紧急采购,3分钟左右您将得到回复。