- 您现在的位置:买卖IC网 > PDF目录1980 > AD73322LARUZ-REEL (Analog Devices Inc)IC PROCESSOR FRONTEND DL 28TSSOP PDF资料下载

参数资料

| 型号: | AD73322LARUZ-REEL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 24/43页 |

| 文件大小: | 0K |

| 描述: | IC PROCESSOR FRONTEND DL 28TSSOP |

| 标准包装: | 2,500 |

| 位数: | 16 |

| 通道数: | 4 |

| 功率(瓦特): | 73mW |

| 电压 - 电源,模拟: | 2.7 V ~ 5.5 V |

| 电压 - 电源,数字: | 2.7 V ~ 5.5 V |

| 封装/外壳: | 28-TSSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 28-TSSOP |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页

AD73322

–30–

REV. B

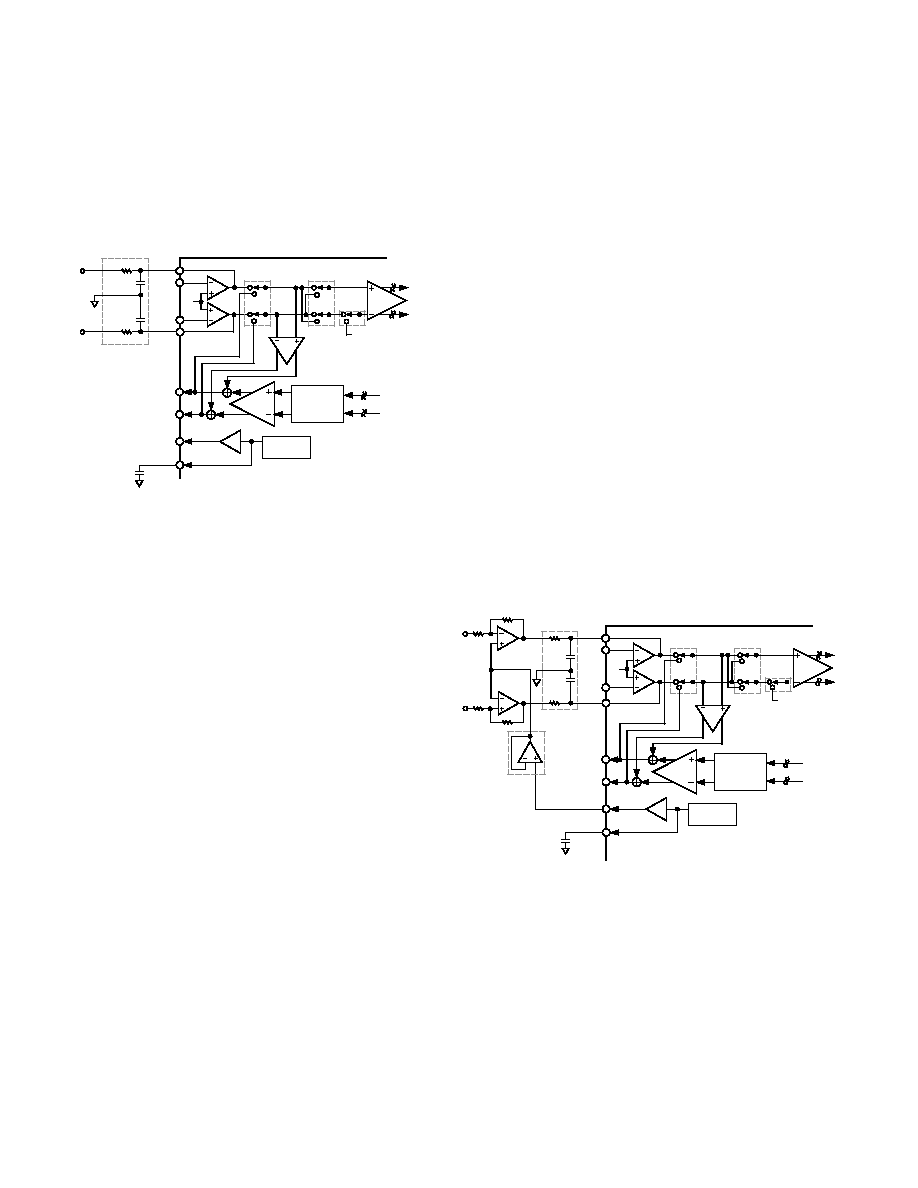

DESIGN CONSIDERATIONS

The AD73322 features both differential inputs and outputs on

each channel to provide optimal performance and avoid com-

mon mode noise. It is also possible to interface either inputs or

outputs in single-ended mode. This section details the choice of

input and output configurations and also gives some tips to-

wards successful configuration of the analog interface sections.

VFBN1

GAIN

1

+6/–15dB

PGA

CONTINUOUS

TIME

LOW-PASS

FILTER

VREF

VINN1

VINP1

VFBP1

VOUTP1

VOUTN1

REFOUT

REFERENCE

AD73322

VREF

ANTI-ALIAS

FILTER

0.047 F

100

0.047 F

100

REFCAP

0.1 F

0/38dB

PGA

Figure 28. Analog Input (DC-Coupled)

Analog Inputs

There are several different ways in which the analog input (en-

coder) section of the AD73322 can be interfaced to external

circuitry. It provides optional input amplifiers which allows

sources with high source impedance to drive the ADC section

correctly. When the input amplifiers are enabled, the input

channel is configured as a differential pair of inverting amplifiers

referenced to the internal reference (REFCAP) level. The in-

verting terminals of the input amplifier pair are designated as

pins VINP1 and VINN1 for Channel 1 (VINP2 and VINN2 for

Channel 2) and the amplifier feedback connections are available

on pins VFBP1 and VFBN1 for Channel 1 (VFBP2 and VFBN2

for Channel 2).

For applications where external signal buffering is required,

the input amplifiers can be bypassed and the ADC driven

directly. When the input amplifiers are disabled, the sigma-

delta modulator’s input section (SC PGA) is accessed di-

rectly through the VFBP1 and VFBN1 pins for Channel 1

(VFBP2 and VFBN2 for Channel 2).

It is also possible to drive the ADCs in either differential or

single-ended modes. If the single-ended mode is chosen it is

possible using software control to multiplex between two single-

ended inputs connected to the positive and negative input pins.

The primary concerns in interfacing to the ADC are firstly to

provide adequate anti-alias filtering and to ensure that the signal

source will drive the switched-capacitor input of the ADC

correctly. The sigma-delta design of the ADC and its over sam-

pling characteristics simplify the antialias requirements but it

must be remembered that the single pole RC filter is primarily

intended to eliminate aliasing of frequencies above the Nyquist

frequency of the sigma-delta modulator’s sampling rate (typi-

cally 2.048 MHz). It may still require a more specific digital

filter implementation in the DSP to provide the final signal

frequency response characteristics. It is recommended that for

optimum performance that the capacitors used for the antialias-

ing filter be of high quality dielectric (NPO). The second issue

mentioned above is interfacing the signal source to the ADC’s

switched capacitor input load. The SC input presents a complex

dynamic load to a signal source, therefore, it is important to

understand that the slew rate characteristic is an important

consideration when choosing external buffers for use with the

AD73322. The internal inverting op amps on the AD73322 are

specifically designed to interface to the ADC’s SC input stage.

The AD73322’s on-chip 38 dB preamplifier can be enabled

when there is not enough gain in the input circuit; the preampli-

fier is configured by bits IGS0-2 of CRD. The total gain must

be configured to ensure that a full-scale input signal produces a

signal level at the input to the sigma-delta modulator of the

ADC that does not exceed the maximum input range.

The dc biasing of the analog input signal is accomplished with

an on-chip voltage reference. If the input signal is not biased at

the internal reference level (via REFOUT), then it must be

ac-coupled with external coupling capacitors. CIN should be

0.1

F or larger. The dc biasing of the input can then be accom-

plished using resistors to REFOUT as in Figures 31 and 32.

VFBN1

GAIN

1

VREF

VINN1

VINP1

VFBP1

VOUTP1

VOUTN1

REFCAP

REFOUT

REFERENCE

0/38dB

PGA

AD73322

VREF

OPTIONAL

BUFFER

ANTI-ALIAS

FILTER

0.1 F

100

0.047

F

0.047

F

+6/–15dB

PGA

CONTINUOUS

TIME

LOW-PASS

FILTER

Figure 29. Analog Input (DC-Coupled) Using External

Amplifiers

相关PDF资料 |

PDF描述 |

|---|---|

| AD73322LYRZ | IC ANALOG FRONT END DUAL 28-SOIC |

| AD73360ARZ | IC PROCESSOR FRONTEND 6CH 28SOIC |

| AD7352YRUZ-500RL7 | IC ADC DUAL 12BIT 3MSPS 16TSSOP |

| AD7356YRUZ-500RL7 | IC ADC DUAL 12BIT 5MSPS 16TSSOP |

| AD7357YRUZ | IC ADC DUAL14BIT 4.2MSPS 16TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD73322LARZ | 功能描述:IC ANALOG FRONT END DUAL 28-SOIC RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| AD73322LARZ-REEL | 制造商:Analog Devices 功能描述:DUAL-CHANNEL, 3 V FRONT-END PROCESSOR FOR GENERAL PURPOSE - Tape and Reel |

| AD73322LAST | 制造商:Rochester Electronics LLC 功能描述:SPEECH AND TELEPHONY CODEC I.C. - Tape and Reel 制造商:Analog Devices 功能描述: |

| AD73322LAST-REEL | 制造商:Analog Devices 功能描述:Audio Codec 2ADC / 2DAC 16-Bit 44-Pin LQFP T/R 制造商:Rochester Electronics LLC 功能描述:SPEECH AND TELEPHONY CODEC I.C. - Tape and Reel |

| AD73322LASTZ | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

发布紧急采购,3分钟左右您将得到回复。