- 您现在的位置:买卖IC网 > PDF目录16854 > AD9517-3A/PCBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9517-3A PDF资料下载

参数资料

| 型号: | AD9517-3A/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 31/80页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9517-3A |

| 设计资源: | AD9517 Eval Brd Schematics AD9517 Gerber Files AD9517-3 BOM |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9517-3A |

| 主要属性: | 2 输入,12 输出,2.0GHz VCO |

| 次要属性: | CMOS,LVPECL 和 LVDS 兼容 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Data Sheet

AD9517-3

Rev. E | Page 37 of 80

DIGITAL LOCK DETECT (DLD)

By selecting the proper output through the mux on each pin,

the DLD function can be made available at the LD, STATUS,

and REFMON pins. The DLD circuit indicates a lock when the

time difference of the rising edges at the PFD inputs is less than

a specified value (the lock threshold). The loss of a lock is

indicated when the time difference exceeds a specified value

(the unlock threshold). Note that the unlock threshold is wider

than the lock threshold, which allows some phase error in

excess of the lock window to occur without chattering on the

lock indicator.

The lock detect window timing depends on three settings:

the digital lock detect window bit (Register 0x018[4]), the

antibacklash pulse width setting (Register 0x017[1:0], see Table 2),

and the lock detect counter (Register 0x018[6:5]). A lock is not

indicated until there is a programmable number of consecutive

PFD cycles with a time difference that is less than the lock detect

threshold. The lock detect circuit continues to indicate a lock

until a time difference greater than the unlock threshold occurs

on a single subsequent cycle. For the lock detect to work properly,

the period of the PFD frequency must be greater than the unlock

threshold. The number of consecutive PFD cycles required for

lock is programmable (Register 0x018[6:5]).

Analog Lock Detect (ALD)

The AD9517 provides an ALD function that can be selected for

use at the LD pin. There are two versions of ALD, as follows:

N-channel open-drain lock detect. This signal requires a

pull-up resistor to the positive supply, VS. The output is

normally high with short, low-going pulses. Lock is indicated

by the minimum duty cycle of the low-going pulses.

P-channel open-drain lock detect. This signal requires a

pull-down resistor to GND. The output is normally low

with short, high-going pulses. Lock is indicated by the

minimum duty cycle of the high-going pulses.

The analog lock detect function requires an R-C filter to

provide a logic level indicating lock/unlock.

AD9517-3

ALD

LD

R1

C

VOUT

R2

VS = 3.3V

064

27

-06

7

Figure 50. Example of Analog Lock Detect Filter,

Using N-Channel Open-Drain Driver

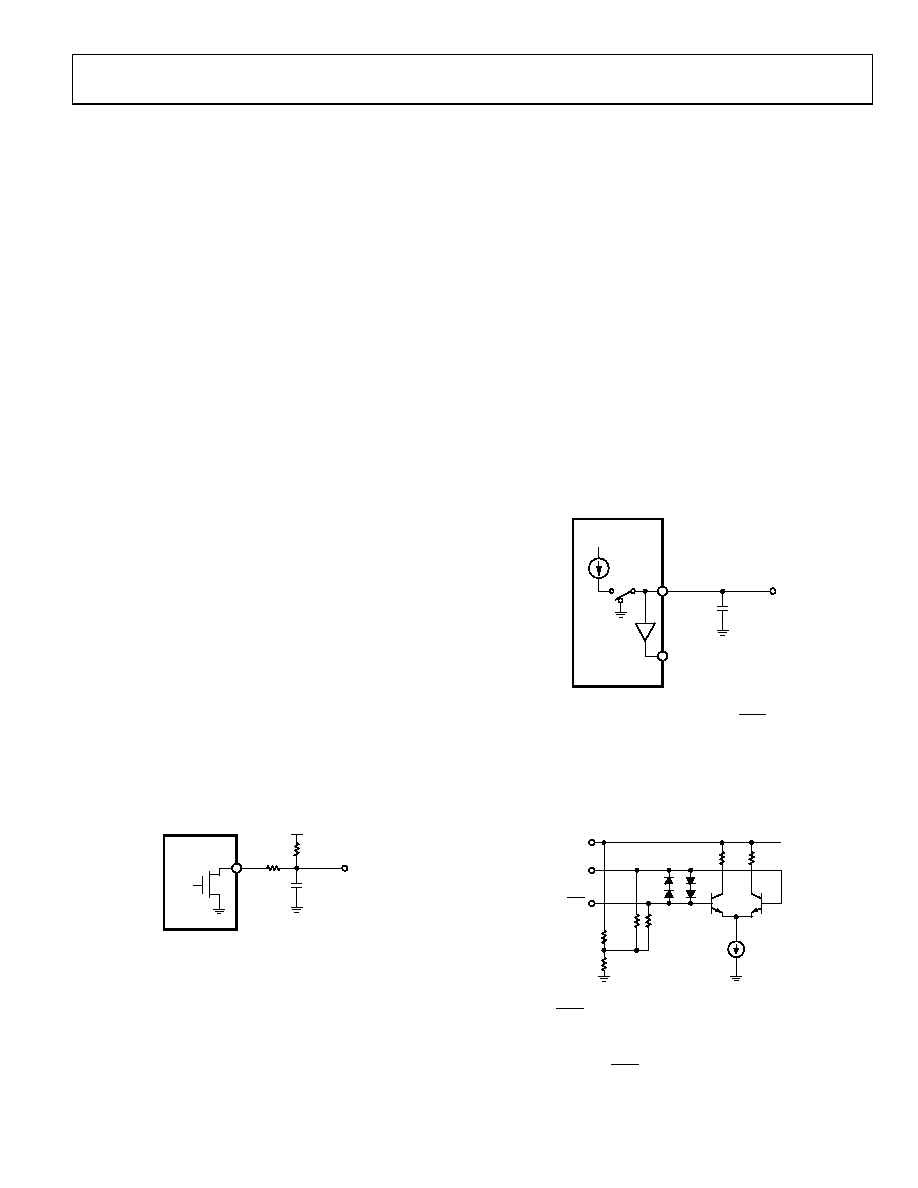

Current Source Digital Lock Detect (DLD)

During the PLL locking sequence, it is normal for the DLD

signal to toggle a number of times before remaining steady

when the PLL is completely locked and stable. There may be

applications where it is desirable to have DLD asserted only

after the PLL is solidly locked. This is made possible by using

the current source lock detect function. This function is set

when it is selected as the output from the LD pin control

(Register 0x01A[5:0]).

The current source lock detect provides a current of 110 μA

when DLD is true, and it shorts to ground when DLD is false.

If a capacitor is connected to the LD pin, it charges at a rate that

is determined by the current source during the DLD true time

but is discharged nearly instantly when DLD is false. By monitoring

the voltage at the LD pin (top of the capacitor), it is possible to

get a logic high level only after the DLD has been true for a

sufficiently long time. Any momentary DLD false resets the

charging. By selecting a properly sized capacitor, it is possible to

delay a lock detect indication until the PLL is stably locked and

the lock detect does not chatter.

The voltage on the capacitor can be sensed by an external

comparator connected to the LD pin. However, there is an

internal LD pin comparator that can be read at the REFMON

pin control (Register 0x01B[4:0]) or the STATUS pin control

(Register 0x017[7:2]) as an active high signal. It is also available

as an active low signal (REFMON, Register 0x01B[4:0] and

STATUS, Register 0x017[7:2]). The internal LD pin comparator

trip point and hysteresis are listed in Table 16.

AD9517-3

LD

REFMON

OR

STATUS

C

VOUT

110A

DLD

LD PIN

COMPARATOR

06

42

7-

06

8

Figure 51. Current Source Lock Detect

External VCXO/VCO Clock Input (CLK/CLK)

CLK is a differential input that can be used as an input to drive

the AD9517 clock distribution section. This input can receive

up to 2.4 GHz. The pins are internally self-biased, and the input

signal should be ac-coupled via capacitors.

VS

CLOCK INPUT

STAGE

CLK

5k

2.5k

0

642

7-

0

32

Figure 52. CLK Equivalent Input Circuit

The CLK/CLK input can be used either as a distribution-only

input (with the PLL off), or as a feedback input for an external

VCO/VCXO using the internal PLL when the internal VCO is

not used. The CLK/CLK input can be used for frequencies up

to 2.4 GHz.

相关PDF资料 |

PDF描述 |

|---|---|

| ADM1191-2ARMZ-R7 | IC PWR MONITOR DGTL ALERT 10MSOP |

| ADCLK954/PCBZ | KIT EVAL CLK BUFF ADCLK954 |

| RNF-100-MINI-SPL-3/32-BK | HEATSHRINK RNF-100 3/32"X65'BLK |

| AD9522-0/PCBZ | BOARD EVAL FOR AD9522-0 CLK GEN |

| EBM22DCMT-S288 | CONN EDGECARD 44POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9517-3BCPZ | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-REEL7 | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-TR | 制造商:Analog Devices 功能描述:12-OUTPUT CLOCK GENERATOR WITH INTEGRATED 2.0 GHZ VCO - Tape and Reel |

| AD9517-4 | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Output Clock Generator with Integrated 1.6 GHz VCO |

| AD9517-4A/PCBZ | 功能描述:BOARD EVALUATION FOR AD9517-4A RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。