- 您现在的位置:买卖IC网 > PDF目录16854 > AD9517-3A/PCBZ (Analog Devices Inc)BOARD EVALUATION FOR AD9517-3A PDF资料下载

参数资料

| 型号: | AD9517-3A/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 78/80页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR AD9517-3A |

| 设计资源: | AD9517 Eval Brd Schematics AD9517 Gerber Files AD9517-3 BOM |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9517-3A |

| 主要属性: | 2 输入,12 输出,2.0GHz VCO |

| 次要属性: | CMOS,LVPECL 和 LVDS 兼容 |

| 已供物品: | 板 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页当前第78页第79页第80页

AD9517-3

Data Sheet

Rev. E | Page 8 of 80

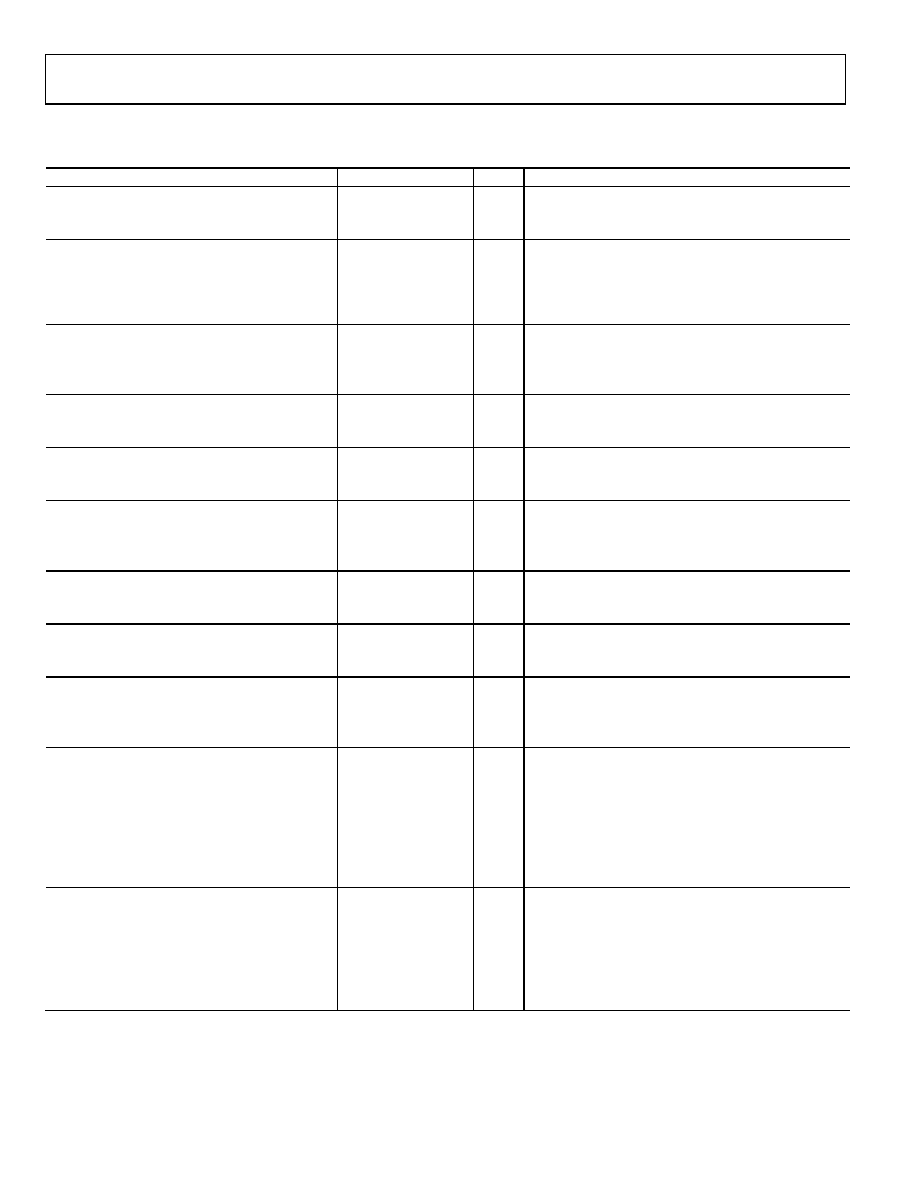

TIMING CHARACTERISTICS

Table 5.

Parameter

Min

Typ

Max

Unit

Test Conditions/Comments

LVPECL

Termination = 50 to VS 2 V; level = 810 mV

Output Rise Time, tRP

70

180

ps

20% to 80%, measured differentially

Output Fall Time, tFP

70

180

ps

80% to 20%, measured differentially

PROPAGATION DELAY, tPECL, CLK-TO-LVPECL

OUTPUT

High Frequency Clock Distribution Configuration

835

995

1180

ps

Clock Distribution Configuration

773

933

1090

ps

Variation with Temperature

0.8

ps/°C

OUTPUT SKEW, LVPECL OUTPUTS1

LVPECL Outputs That Share the Same Divider

5

15

ps

LVPECL Outputs on Different Dividers

13

40

ps

All LVPECL Outputs Across Multiple Parts

220

ps

LVDS

Termination = 100 differential; 3.5 mA

Output Rise Time, tRL

170

350

ps

20% to 80%, measured differentially2

Output Fall Time, tFL

160

350

ps

20% to 80%, measured differentially2

PROPAGATION DELAY, tLVDS, CLK-TO-LVDS OUTPUT

Delay off on all outputs

For All Divide Values

1.4

1.8

2.1

ns

Variation with Temperature

1.25

ps/°C

OUTPUT SKEW, LVDS OUTPUTS1

Delay off on all outputs

LVDS Outputs That Share the Same Divider

6

62

ps

LVDS Outputs on Different Dividers

25

150

ps

All LVDS Outputs Across Multiple Parts

430

ps

CMOS

Termination = open

Output Rise Time, tRC

495

1000

ps

20% to 80%; CLOAD = 10 pF

Output Fall Time, tFC

475

985

ps

80% to 20%; CLOAD = 10 pF

PROPAGATION DELAY, tCMOS, CLK-TO-CMOS OUTPUT

Fine delay off

For All Divide Values

1.6

2.1

2.6

ns

Variation with Temperature

2.6

ps/°C

OUTPUT SKEW, CMOS OUTPUTS1

Fine delay off

CMOS Outputs That Share the Same Divider

4

66

ps

All CMOS Outputs on Different Dividers

28

180

ps

All CMOS Outputs Across Multiple Parts

675

ps

DELAY ADJUST3

LVDS and CMOS

Shortest Delay Range4

Register 0x0A1 (0x0A4, 0x0A7, 0x0AA), Bits[5:0] = 101111b

Zero Scale

50

315

680

ps

Register 0x0A2 (0x0A5, 0x0A8, 0x0AB), Bits[5:0] = 000000b

Full Scale

540

880

1180

ps

Register 0x0A2 (0x0A5, 0x0A8, 0x0AB), Bits[5:0] = 101111b

Longest Delay Range4

Register 0x0A1 (0x0A4, 0x0A7, 0x0AA), Bits[5:0] = 000000b

Zero Scale

200

570

950

ps

Register 0x0A2 (0x0A5, 0x0A8, 0x0AB), Bits[5:0] = 000000b

Quarter Scale

1.72

2.31

2.89

ns

Register 0x0A2 (0x0A5, 0x0A8, 0x0AB), Bits[5:0] = 001100b

Full Scale

5.7

8.0

10.1

ns

Register 0x0A2 (0x0A5, 0x0A8, 0x0AB), Bits[5:0] = 101111b

Delay Variation with Temperature

Short Delay Range5

Zero Scale

0.23

ps/°C

Full Scale

0.02

ps/°C

Long Delay Range5

Zero Scale

0.3

ps/°C

Full Scale

0.24

ps/°C

1

This is the difference between any two similar delay paths while operating at the same voltage and temperature.

2

Corresponding CMOS drivers set to A for noninverting and B for inverting.

3

The maximum delay that can be used is a little less than one-half the period of the clock. A longer delay disables the output.

4

Incremental delay; does not include propagation delay.

5

All delays between zero scale and full scale can be estimated by linear interpolation.

相关PDF资料 |

PDF描述 |

|---|---|

| ADM1191-2ARMZ-R7 | IC PWR MONITOR DGTL ALERT 10MSOP |

| ADCLK954/PCBZ | KIT EVAL CLK BUFF ADCLK954 |

| RNF-100-MINI-SPL-3/32-BK | HEATSHRINK RNF-100 3/32"X65'BLK |

| AD9522-0/PCBZ | BOARD EVAL FOR AD9522-0 CLK GEN |

| EBM22DCMT-S288 | CONN EDGECARD 44POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9517-3BCPZ | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-REEL7 | 制造商:Analog Devices 功能描述: |

| AD9517-3BCPZ-TR | 制造商:Analog Devices 功能描述:12-OUTPUT CLOCK GENERATOR WITH INTEGRATED 2.0 GHZ VCO - Tape and Reel |

| AD9517-4 | 制造商:AD 制造商全称:Analog Devices 功能描述:12-Output Clock Generator with Integrated 1.6 GHz VCO |

| AD9517-4A/PCBZ | 功能描述:BOARD EVALUATION FOR AD9517-4A RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

发布紧急采购,3分钟左右您将得到回复。