- 您现在的位置:买卖IC网 > PDF目录16848 > AD9524/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9524 PDF资料下载

参数资料

| 型号: | AD9524/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 11/56页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9524 |

| 设计资源: | AD9524 Schematic AD9524 BOM AD9524 Gerber Files |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9524 |

| 主要属性: | USB 供电或外部电源 |

| 次要属性: | 状态 LED |

| 已供物品: | 板 |

| 配用: | AD9524BCPZ-ND - IC INTEGER-N CLCK GEN 48LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

Data Sheet

AD9524

Rev. E | Page 19 of 56

THEORY OF OPERATION

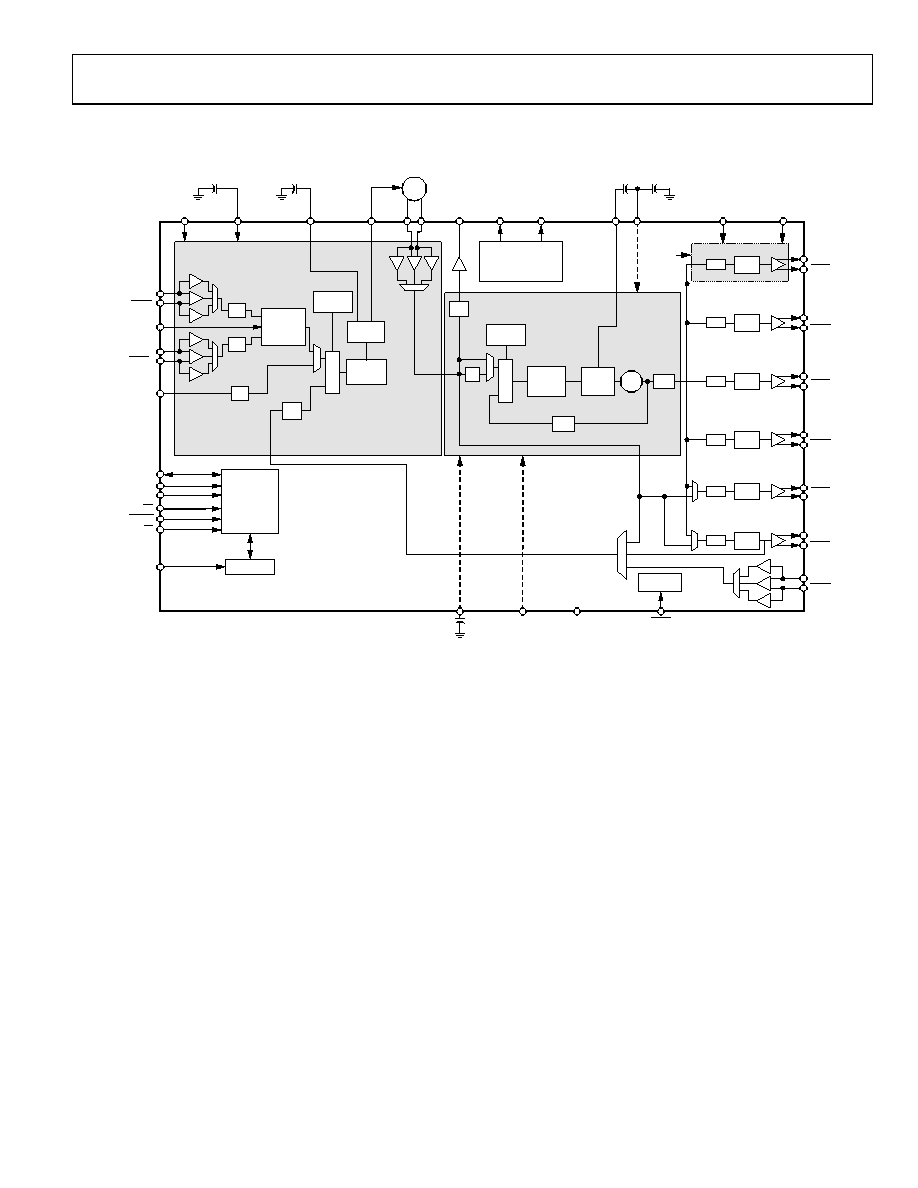

DETAILED BLOCK DIAGRAM

CHARGE

PUMP

×2

÷D1

VCXO

SWITCH-

OVER

CONTROL

RESYNCH

÷M1

STATUS MONITOR

LOCK DETECT/

SERIAL PORT

ADDRESS

CONTROL

INTERFACE

(SPI AND I2C)

SCLK/SCL

SDO

SDIO/SDA

÷N2

PLL2

LDO_PLL2

LOOP

FILTER

TO SYNC

LOOP

FILTER

CHARGE

PUMP

PLL1

LOCK

DETECT

LOCK

DETECT

P

F

D

ZD_IN

PD

RESET

SYNC

÷D

Δt

EDGE

÷D

Δt

EDGE

÷D

Δt

EDGE

÷D

Δt

EDGE

÷D

Δt

EDGE

÷D

Δt

EDGE

SYNC

SIGNAL

PLL1_OUT

VDD1.8_OUT[X:Y]

REFA

REFB

AD9524

REF_SEL

STATUS0/

SP0

STATUS1/

SP1

EEPROM

EEPROM_SEL

LF2_EXT_CAP

LF1_EXT_CAP

REF_TEST

OSC_CTRL

OSC_IN

CS

÷R

÷N1

LDO_PLL1

LDO_VCO

VDD3_OUT[X:Y]

VDD3_PLL1

VDD3_PLL2

NC

VCO

P

F

D

OUT5

OUT4

OUT3

OUT2

OUT1

OUT0

09081-

020

Figure 22. Top Level Diagram

OVERVIEW

The AD9524 is a clock generator that employs integer-N-based

phase-locked loops (PLL). The device architecture consists of

two cascaded PLL stages. The first stage, PLL1, consists of an

integer division PLL that uses an external voltage-controlled

crystal oscillator (VCXO) of up to 250 MHz. PLL1 has a narrow-

loop bandwidth that provides initial jitter cleanup of the input

reference signal. The second stage, PLL2, is a frequency

multiplying PLL that translates the first stage output frequency

to a range of 3.6 GHz to 4.0 GHz. PLL2 incorporates an integer-

based feedback divider that enables integer frequency multipli-

cation. Programmable integer dividers (1 to 1024) follow PLL2,

establishing a final output frequency of 1 GHz or less.

The AD9524 includes reference signal processing blocks that

enable a smooth switching transition between two reference

inputs. This circuitry automatically detects the presence of the

reference input signals. If only one input is present, the device

uses it as the active reference. If both are present, one becomes

the active reference and the other becomes the backup reference.

If the active reference fails, the circuitry automatically switches

to the backup reference (if available), making it the new active

reference. A register setting determines what action to take if the

failed reference is once again available: either stay on Reference B

or revert to Reference A. If neither reference can be used, the

AD9524 supports a holdover mode. A reference select pin

(REF_SEL, Pin 45) is available to manually select which input

reference is active (see Table 43). The accuracy of the holdover

is dependent on the external VCXO frequency stability at half

supply voltage.

Any of the divider settings are programmable via the serial

programming port, enabling a wide range of input/output

frequency ratios under program control. The dividers also

include a programmable delay to adjust timing of the output

signals, if required.

The output is compatible with LVPECL, LVDS, or HSTL logic

levels (see the Input/Output Termination Recommendations

section); however, the AD9524 is implemented only in CMOS.

The loop filters of each PLL are integrated and programmable.

Only a single external capacitor for each of the two PLL loop

filters is required.

The AD9524 operates over the extended industrial temperature

range of 40°C to +85°C.

相关PDF资料 |

PDF描述 |

|---|---|

| V150C12E150BF | CONVERTER MOD DC/DC 12V 150W |

| 0982660986 | CBL 27PS 0.5MM JMPR TYPE D 1.18" |

| H6MMH-3006G | DIP CABLE - HDM30H/AE30G/HDM30H |

| TCMD-25-T-02.00-01-N | CABLE ASSEM 2MM 50POS M-F 2" |

| GEC17DRXI-S734 | CONN EDGECARD 34POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9525 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Jitter Clock Generator with Eight LVPECL Outputs |

| AD9525/PCBZ | 功能描述:时钟和定时器开发工具 Evaluation kit 2950MHz VCO installed RoHS:否 制造商:Texas Instruments 产品:Evaluation Modules 类型:Clock Conditioners 工具用于评估:LMK04100B 频率:122.8 MHz 工作电源电压:3.3 V |

| AD9525/PCBZ-VCO | 功能描述:时钟和定时器开发工具 Evaluation kit CRO29508 VCO installed RoHS:否 制造商:Texas Instruments 产品:Evaluation Modules 类型:Clock Conditioners 工具用于评估:LMK04100B 频率:122.8 MHz 工作电源电压:3.3 V |

| AD9525BCPZ | 功能描述:时钟发生器及支持产品 High performance clock distributor Exter RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| AD9525BCPZ-REEL7 | 功能描述:时钟发生器及支持产品 High performance clock distributor Exter RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。