- 您现在的位置:买卖IC网 > PDF目录16848 > AD9524/PCBZ (Analog Devices Inc)BOARD EVAL FOR AD9524 PDF资料下载

参数资料

| 型号: | AD9524/PCBZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 49/56页 |

| 文件大小: | 0K |

| 描述: | BOARD EVAL FOR AD9524 |

| 设计资源: | AD9524 Schematic AD9524 BOM AD9524 Gerber Files |

| 标准包装: | 1 |

| 主要目的: | 计时,时钟发生器 |

| 嵌入式: | 否 |

| 已用 IC / 零件: | AD9524 |

| 主要属性: | USB 供电或外部电源 |

| 次要属性: | 状态 LED |

| 已供物品: | 板 |

| 配用: | AD9524BCPZ-ND - IC INTEGER-N CLCK GEN 48LFCSP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页

Data Sheet

AD9524

Rev. E | Page 53 of 56

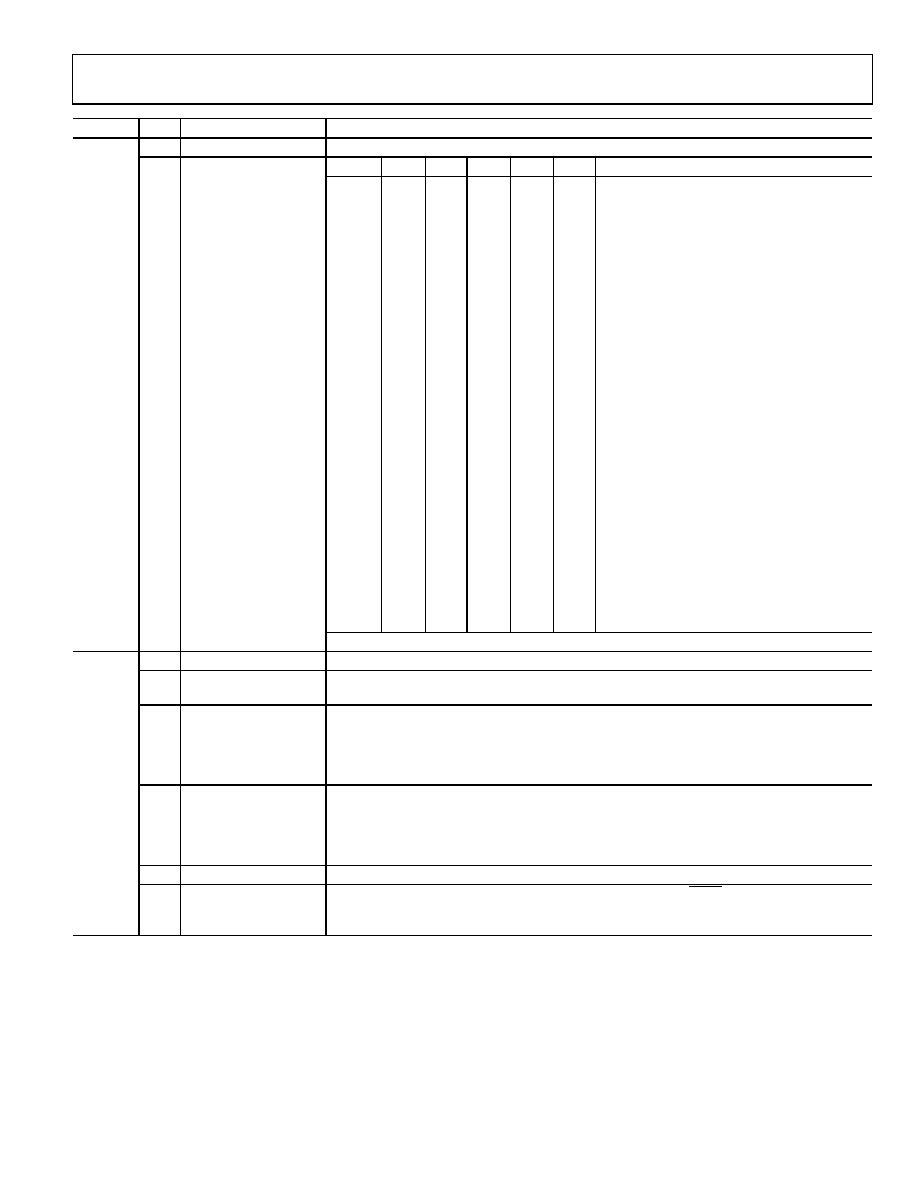

Address

Bits

Bit Name

Description

0x231

[7:6]

Reserved

Reserved.

[5:0]

Status Monitor 1 control

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Muxout

0

GND

0

1

PLL1 and PLL2 locked

0

1

0

PLL1 locked

0

1

PLL2 locked

0

1

0

Both references are missing (REFA and REFB)

0

1

0

1

Both references are missing and PLL2 is locked

0

1

0

REFB selected (applies only to auto select mode)

0

1

REFA is OK

0

1

0

REFB is OK

0

1

0

1

REF_TEST is OK

0

1

0

1

0

VCXO is OK

0

1

0

1

PLL1 feedback is OK

0

1

0

PLL2 reference clock is OK

0

1

0

1

Reserved

0

1

0

REFA and REFB are OK

0

1

All clocks are OK (except REF_TEST)

0

1

0

GND

0

1

0

1

GND

0

1

0

1

0

GND

0

1

0

1

GND

0

1

0

1

0

PLL2 feedback is divide-by-2

0

1

0

1

0

1

PLL2 PFD down divide-by-2

0

1

0

1

0

PLL2 REF divide-by-2

0

1

0

1

PLL2 PFD up divide-by-2

Note that all bit combinations after 010111 are reserved.

0x232

[7:5]

Reserved

Reserved.

4

Enable Status_EEPROM

on STATUS0 pin

Enables the EEPROM status on the STATUS0 pin.

1: enable status.

3

STATUS1 pin divider

enable

Enables a divide-by-4 on the STATUS1 pin, allowing dynamic signals to be viewed at a lower

frequency (such as the PFD input clocks). Not to be used with dc states on the status pins,

which occur when the settings of Register 0x231, Bits[5:0] are in the range of 000000 to 001111.

1: enabled.

0: disabled.

2

STATUS0 pin divider

enable

Enables a divide-by-4 on the STATUS0 pin, allowing dynamic signals to be viewed at a lower

frequency (such as the PFD input clocks). Not to be used with dc states on the status pins,

which occur when the settings of Register 0x230, Bits[5:0] are in the range of 000000 to 001111.

1: enable.

0: disable.

1

Reserved

Reserved.

0

Sync dividers

(manual control)

Set bit to put dividers in sync; clear bit to release. Functions like SYNC pin low.

1: sync.

0: normal.

相关PDF资料 |

PDF描述 |

|---|---|

| V150C12E150BF | CONVERTER MOD DC/DC 12V 150W |

| 0982660986 | CBL 27PS 0.5MM JMPR TYPE D 1.18" |

| H6MMH-3006G | DIP CABLE - HDM30H/AE30G/HDM30H |

| TCMD-25-T-02.00-01-N | CABLE ASSEM 2MM 50POS M-F 2" |

| GEC17DRXI-S734 | CONN EDGECARD 34POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9525 | 制造商:AD 制造商全称:Analog Devices 功能描述:Low Jitter Clock Generator with Eight LVPECL Outputs |

| AD9525/PCBZ | 功能描述:时钟和定时器开发工具 Evaluation kit 2950MHz VCO installed RoHS:否 制造商:Texas Instruments 产品:Evaluation Modules 类型:Clock Conditioners 工具用于评估:LMK04100B 频率:122.8 MHz 工作电源电压:3.3 V |

| AD9525/PCBZ-VCO | 功能描述:时钟和定时器开发工具 Evaluation kit CRO29508 VCO installed RoHS:否 制造商:Texas Instruments 产品:Evaluation Modules 类型:Clock Conditioners 工具用于评估:LMK04100B 频率:122.8 MHz 工作电源电压:3.3 V |

| AD9525BCPZ | 功能描述:时钟发生器及支持产品 High performance clock distributor Exter RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| AD9525BCPZ-REEL7 | 功能描述:时钟发生器及支持产品 High performance clock distributor Exter RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。