参数资料

| 型号: | AD9577BCPZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 29/44页 |

| 文件大小: | 0K |

| 描述: | IC CLK GEN PLL DUAL 40LFCSP |

| 标准包装: | 2,500 |

| 系列: | PCI Express® (PCIe) |

| 类型: | 扇出缓冲器(分配),网络时钟发生器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,PCI Express(PCIe),SONET/SDH |

| 输入: | 时钟,晶体 |

| 输出: | LVCMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:5 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 637.5MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-WQ(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

Data Sheet

AD9577

Rev. 0 | Page 35 of 44

MARGINING

By asserting the MARGIN pin, a second full frequency map can

be applied to the output ports. The values for the Na, V0, D0,

V1, and D1 parameters, and the Nb, FRAC, MOD, V2, D2, V3,

D3 parameters must be programmed over the I2C, although default

values exist. There are some limitations: the output buffer signal

formats cannot be changed, and the PLL2 fractional-N settings,

such as power-down of the SDM, and bleed settings cannot be

changed. The margining feature can be used to set higher than

nominal frequencies on each of the ports to test system robustness.

When the MARGIN pin signal level is changed, a new frequency

acquisition is performed.

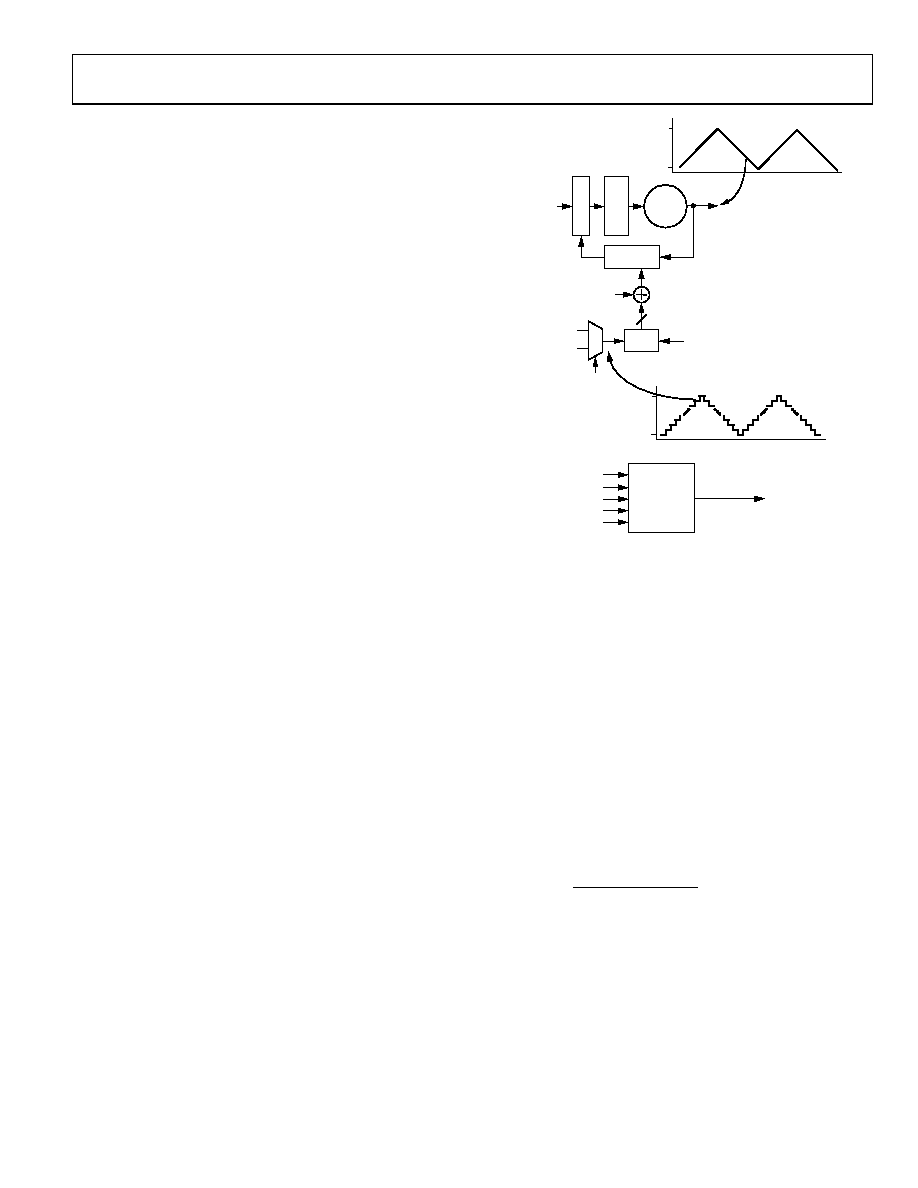

SPREAD SPECTRUM CLOCK GENERATION (SSCG)

By asserting the SSCG (spread spectrum clock generator) pin,

PLL2 operates in spread spectrum mode, and the output

frequency modulates with a triangular profile. As the clock

signal energy spreads out over a range of frequencies, it reduces

the peak power at any one frequency when observed with a

spectrum analyzer through a resolution bandwidth filter. This

result improves the radiated emissions from the part and from

the devices that receive its clock.

The triangular-wave modulation is implemented by controlling

the divide ratio of the feedback divider. This is achieved by

ramping the fractional word to the SDM. Figure 43 shows an

example implementation. The PFD frequency, fPFD, is 25 MHz.

The starting VCO frequency, fVCO, is 25 MHz × (99 + 3072/4096),

giving 2.49375 GHz. By continuously ramping the FRAC word

down and up, this frequency is periodically reduced to 25 MHz ×

(99 + 1029/4096) = 2.481281 GHz. This results in a triangular

frequency modulation profile, with a peak downspread (that is,

peak percentage frequency reduction) of 0.5%. By controlling

the step size, number of steps, and the step rate, the modulation

frequency is adjusted.

fPFD

VCO

2.15GHz

TO

2.55GHz

P

F

D/

CP

TH

IR

D

O

RDE

R

L

P

F

DIVIDE BY

80 TO 131

FEEDBACK

DIVIDER

NB

SDM

3-BIT

0

1

FRAC

FRAC_TRIWAVE

SSCG

MOD

CKDIV

FRAC

FRACSTEP

NUMSTEPS

SSCG

TRIWAVE

GENERATOR

FRAC_TRIWAVE

fVCO

fVCO – 0.5%

TIME

VCO

FREQUENCY

TIME

FRAC_TRIWAVE = 3072

FRAC_TRIWAVE = 1029

092

84-

0

48

Figure 43. Spread Spectrum Clock Generator with Triangular Wave

Modulation, fPFD = 25 MHz

Basic Spread Spectrum Programming

The SSCG is highly programmable; however, most applications

require that the frequency modulation rate be between 30 kHz

and 33 kHz and that the peak frequency deviation be 0.5%

downspread. The AD9577 supports downspread only, with a

maximum deviation of 0.5%.

The key parameters (which are not themselves registers) that

define the frequency modulation profile include the following:

fMOD, which is the frequency of the modulation waveform.

FracRange, which determines the peak frequency deviation

by setting the maximum change in the FRAC value from

the nominal.

The following equations determine the value of these parameters:

FracRange = FracStep × NumSteps

(12)

CkDiv

NumSteps

f

PFD

MOD

×

=

2

(13)

where the following are programmable registers:

NumSteps is the number of fractional word steps in half the

triwave period.

FracStep is the value of the fractional word increment/

decrement, while traversing the tri-wave.

CkDiv is the integer value by which the reference clock

frequency is divided to determine the update rate of the

triangular-wave generator, that is, the step update rate.

fPFD is the PFD frequency.

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/24FG11PA | CONN RCPT 11POS JAM NUT W/PINS |

| VE-J5J-MW-B1 | CONVERTER MOD DC/DC 36V 100W |

| VE-J4D-MX-F4 | CONVERTER MOD DC/DC 85V 75W |

| LT8500IUHH#PBF | IC PWM GENERATOR 56-QFN |

| VE-J4F-MX-F3 | CONVERTER MOD DC/DC 72V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9577-EVALZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Clock Generator with Dual PLLs |

| AD9578BCPZ | 功能描述:IC PLL CLOCK GEN 20MHZ 48LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 类型:* PLL:带旁路 输入:LVCMOS,LVDS,LVPECL,晶体 输出:HCSL,LVCMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:2:5 差分 - 输入:输出:是/是 频率 - 最大值:919MHz 分频器/倍频器:是/无 电压 - 电源:2.375 V ~ 3.63 V 工作温度:-25°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP-VQ(7x7) 标准包装:1 |

| AD9578BCPZ-REEL7 | 功能描述:IC PLL CLOCK GEN 20MHZ 48LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:有效 类型:* PLL:带旁路 输入:LVCMOS,LVDS,LVPECL,晶体 输出:HCSL,LVCMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:2:5 差分 - 输入:输出:是/是 频率 - 最大值:919MHz 分频器/倍频器:是/无 电压 - 电源:2.375 V ~ 3.63 V 工作温度:-25°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP-VQ(7x7) 标准包装:1 |

| AD95S08KAC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:THYRISTOR MODULE|DOUBLER|HALF-CNTLD|POSITIVE|15V V(RRM)|95A I(T) |

| AD95S08KAF | 制造商:未知厂家 制造商全称:未知厂家 功能描述:THYRISTOR MODULE|DOUBLER|HALF-CNTLD|POSITIVE|15V V(RRM)|95A I(T) |

发布紧急采购,3分钟左右您将得到回复。