参数资料

| 型号: | AD9577BCPZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 33/44页 |

| 文件大小: | 0K |

| 描述: | IC CLK GEN PLL DUAL 40LFCSP |

| 标准包装: | 2,500 |

| 系列: | PCI Express® (PCIe) |

| 类型: | 扇出缓冲器(分配),网络时钟发生器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,PCI Express(PCIe),SONET/SDH |

| 输入: | 时钟,晶体 |

| 输出: | LVCMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:5 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 637.5MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-WQ(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页当前第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

Data Sheet

AD9577

Rev. 0 | Page 39 of 44

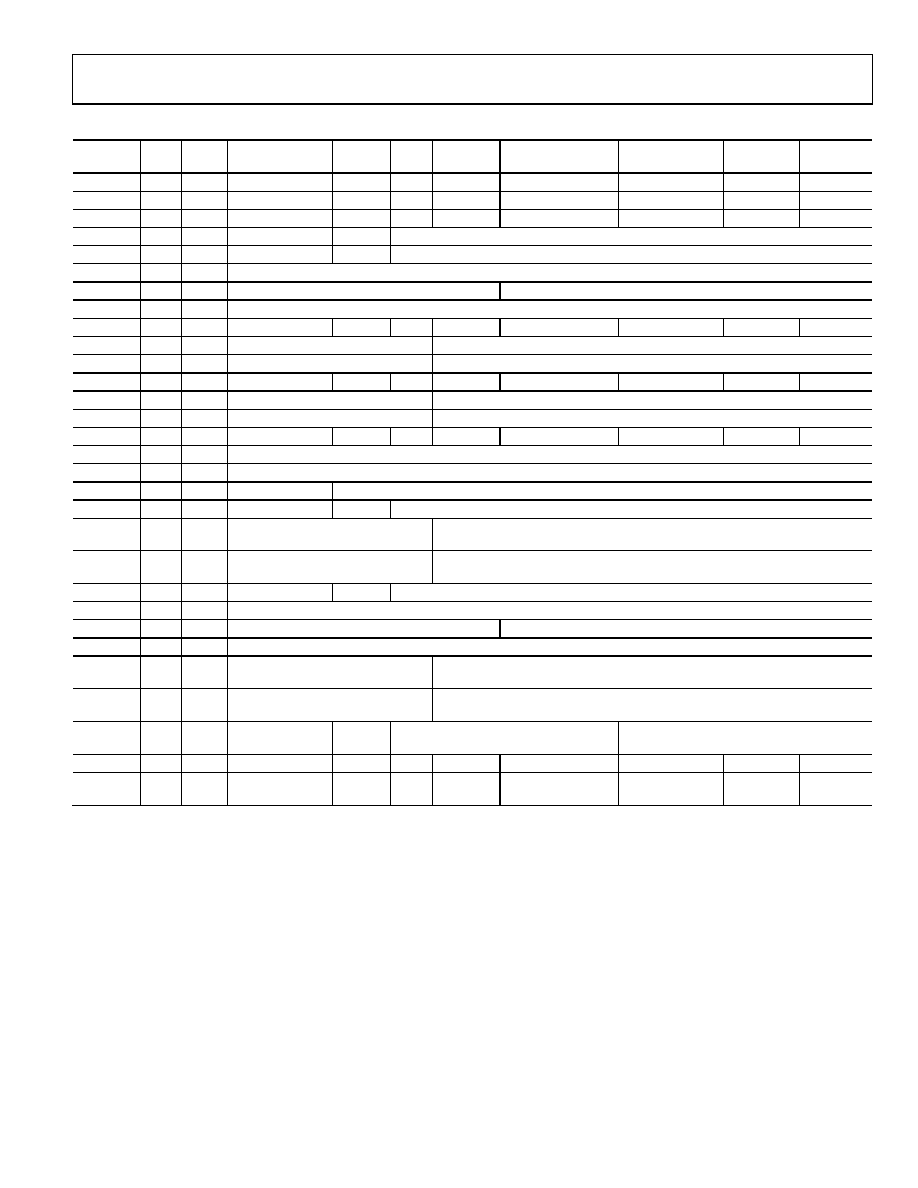

Table 30. Internal Register Map

Register

Name

R/W

Addr

D7

D6

D5

D4

D3

D2

D1

D0

C0

W

0x40

0

EnI2C

0

X0

W

0x1F

0

NewAcq

BP0

W

0x11

0

Bleed

PDCH1

PDCH0

AF0

W

0x18

0

Na[5:0], PLL1 feedback divider ratio

BF3

W

0x1C

0

Nb[5:0], PLL2 feedback divider ratio

BF0

W

0x19

FRAC[11:4], SDM fractional word

BF1

W

0x1A

FRAC[3:0], SDM fractional word

MOD[11:8], SDM modulus

BF2

W

0x1B

MOD[7:0], SDM modulus

ABF0

W

0x1D

1

0

PD_SDM

0

ADV0

W

0x22

V0[2:0], Channel 0 VCO divider

D0[4:0], Channel 0 output divider value

ADV1

W

0x23

V1[2:0], Channel 1 VCO divider

D1[4:0], Channel 1 output divider value

ADV2

W

0x24

0

SyncCh01

BDV0

W

0x25

V2[2:0], Channel 2 VCO divider

D2[4:0], Channel 2 output divider value

BDV1

W

0x26

V3[2:0], Channel 3 VCO divider

D3[4:0], Channel 3 output divider value

BDV2

W

0x27

0

SyncCh23

BS1

W

0x2A

FracStep[7:0], SSCG fractional step size

BS2

W

0x2B

NumSteps[8:1], number of fractional word increments/decrements per half triangular-wave cycle

BS3

W

0x2C

NumSteps[0]

CkDiv[6:0], reference divider output is divided by this integer to determine SSCG update rate

AM0

W

0x30

0

Na[5:0], PLL1 feedback divider ratio divider; MARGIN = 1

AM1

W

0x31

V0[2:0], Channel 0 VCO divider;

MARGIN = 1

D0[4:0], Channel 0 output divider value; MARGIN = 1

AM2

W

0x32

V1[2:0], Channel 1 VCO divider;

MARGIN = 1

D1[4:0], Channel 1 output divider value; MARGIN = 1

BM0

W

0x33

0

Nb[5:0], PLL2 feedback divider ratio divider; MARGIN = 1

BM1

W

0x34

FRAC[11:4], SDM fractional word; MARGIN = 1

BM2

W

0x35

FRAC[3:0], SDM fractional word; MARGIN = 1

MOD[11:8], SDM modulus; MARGIN = 1

BM3

W

0x36

MOD[7:0], SDM modulus; MARGIN = 1

BM4

W

0x37

V3[2:0], Channel 3 VCO divider;

MARGIN = 1

D3[4:0], Channel 3 output divider value; MARGIN = 1

BM5

W

0x38

V2[2:0], Channel 2 VCO divider;

MARGIN = 1

D2[4:0], Channel 2 output divider value; MARGIN = 1

DR1

W

0x3A

PDCH3

PDCH2

FORMAT2[2:0], output format selection

for PLL2 (see

FORMAT1[2:0], output format selection for

PLL1 (see

DR2

W

0x3B

0

PDRefOut

G0

W

0x3D

0

PDPLL1, power-

down PLL1

PDPLL2, power-

down PLL2

R; 0 =

divide by 1

0

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/24FG11PA | CONN RCPT 11POS JAM NUT W/PINS |

| VE-J5J-MW-B1 | CONVERTER MOD DC/DC 36V 100W |

| VE-J4D-MX-F4 | CONVERTER MOD DC/DC 85V 75W |

| LT8500IUHH#PBF | IC PWM GENERATOR 56-QFN |

| VE-J4F-MX-F3 | CONVERTER MOD DC/DC 72V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9577-EVALZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Clock Generator with Dual PLLs |

| AD9578BCPZ | 功能描述:IC PLL CLOCK GEN 20MHZ 48LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 类型:* PLL:带旁路 输入:LVCMOS,LVDS,LVPECL,晶体 输出:HCSL,LVCMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:2:5 差分 - 输入:输出:是/是 频率 - 最大值:919MHz 分频器/倍频器:是/无 电压 - 电源:2.375 V ~ 3.63 V 工作温度:-25°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP-VQ(7x7) 标准包装:1 |

| AD9578BCPZ-REEL7 | 功能描述:IC PLL CLOCK GEN 20MHZ 48LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:有效 类型:* PLL:带旁路 输入:LVCMOS,LVDS,LVPECL,晶体 输出:HCSL,LVCMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:2:5 差分 - 输入:输出:是/是 频率 - 最大值:919MHz 分频器/倍频器:是/无 电压 - 电源:2.375 V ~ 3.63 V 工作温度:-25°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP-VQ(7x7) 标准包装:1 |

| AD95S08KAC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:THYRISTOR MODULE|DOUBLER|HALF-CNTLD|POSITIVE|15V V(RRM)|95A I(T) |

| AD95S08KAF | 制造商:未知厂家 制造商全称:未知厂家 功能描述:THYRISTOR MODULE|DOUBLER|HALF-CNTLD|POSITIVE|15V V(RRM)|95A I(T) |

发布紧急采购,3分钟左右您将得到回复。