参数资料

| 型号: | AD9577BCPZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 30/44页 |

| 文件大小: | 0K |

| 描述: | IC CLK GEN PLL DUAL 40LFCSP |

| 标准包装: | 2,500 |

| 系列: | PCI Express® (PCIe) |

| 类型: | 扇出缓冲器(分配),网络时钟发生器,多路复用器 |

| PLL: | 是 |

| 主要目的: | 以太网,PCI Express(PCIe),SONET/SDH |

| 输入: | 时钟,晶体 |

| 输出: | LVCMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:5 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 637.5MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-WQ(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页当前第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页

AD9577

Data Sheet

Rev. 0 | Page 36 of 44

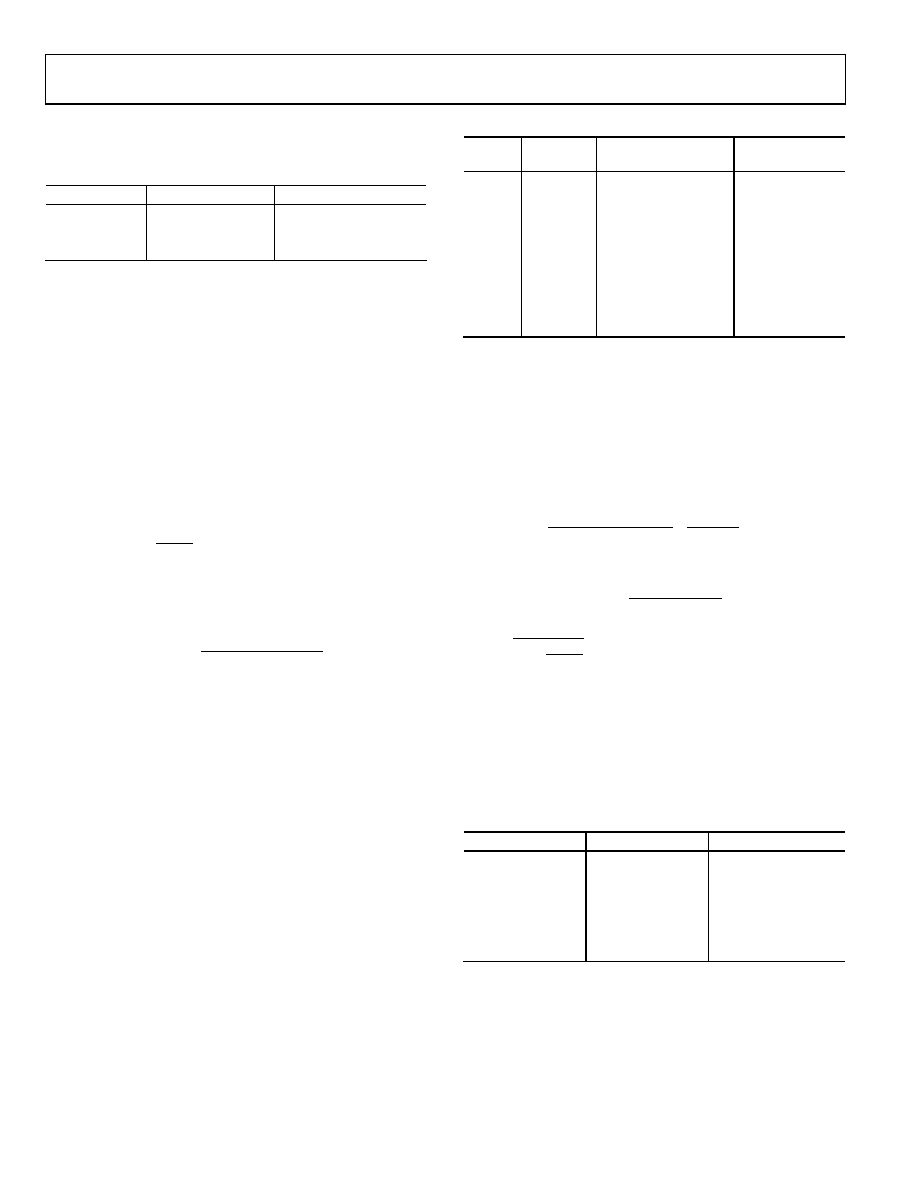

Table 27. CkDiv and FracStep Values Used in Worked Example

CkDiv

Ideal

FracStep

Rounded FracStep

Table 26 shows the relevant register names and programmable

ranges.

Table 26. Registers Used to Program SSCG Operation

Parameter

FracStep Error

2

1.5675

2

21.6%

Register Name

Range

NumSteps

3

2.35125

2

17.6%

BS2[7:0], BS3[7]

+1 to +511

FracStep

4

3.135

3

4.5%

BS1[7:0]

128 to 0

5

3.91875

4

2.0%

CkDiv

BS3[6:0]

+2 to +127

6

4.7025

5

6.0%

7

5.48625

5

9.7%

Because the register values need to be expressed as integers,

there are no guaranteed exact solutions; therefore, some

approximations and trade-offs must be made. The fact that

neither FracRange nor fMOD needs to be exact is exploited.

Note that the SSCG pin must be toggled every time the SSCG

parameters are adjusted for the changes to take effect.

8

6.27

6

4.5%

9

7.05375

7

0.77%

10

7.8375

8

2.0%

Both CkDiv and NumSteps must be integers. To minimize error,

CkDiv = 9 and FracStep = 7 was chosen. With a target for

FracRange = 313.5, Equation 12 is used to find the ideal value of

NumSteps = 44.79, which is rounded to 45. From Equation 12,

the actual used value for FracRange is

Worked Example: Programming for fMOD = 31.25 kHz,

Downspread = 0.5%, fPFD = 25 MHz

Assume Nb = 100, MOD = 625, and FRAC = 198. In addition, a

large number of frequency steps are desired to cover 0.5%. The

objective is to find values for FracStep, NumSteps, and CkDiv

that result in the required frequency modulation profile.

FracRange = 7 × 45 = 315

The accuracy of this solution needs to be verified. Putting the

derived values into Equation 13 gives

The total feedback divider ratio is

kHz

30.86

9

45

2

MHz

25

2

=

×

=

×

=

CkDiv

NumSteps

f

PFD

MOD

NTOT = Nb +

MOD

FRAC

= 100 + 198/625 = 62,698/625

FracRange is set to 0.5% of 62,698, which results in an ideal

value of 313.5.

By rearranging Equation 12 and Equation 13, it results in

×

=

PFD

MOD

f

FracRange

CkDiv

FracStep

2

(14)

In addition, the percentage frequency deviation is obtained as

%

502

.

0

625

62698

625

315

100

=

×

×

=

×

=

TOT

N

MOD

FracRange

eviation

FrequencyD

The fMOD and the percentage frequency deviation are very close to

the target values. The register settings required for this example

are detailed in Table 29.

Putting in the values for FracRange, fMOD, and fPFD from the

previous information, the following results:

FracStep = CkDiv × (0.78375)

(15)

SSCG Register Summary

An approximate solution must be found to Equation 15 that

produces an integer value for CkDiv, which gives a value that is

very close to an integer for FracStep. In this case, considering

CkDiv values in the range of 2 to 10 gives the FracStep values

shown in Table 27.

Table 28 summarizes the programmable registers required to set

up SSCG.

Table 28. Register Values for SSCG

Parameter

Register Names

Range

NumSteps

BS2[7:0], BS3[7]

+1 to +511

FracStep

BS1[7:0]

128 to 0

CkDiv

BS3[6:0]

+2 to +127

FRAC

BF0[7:0], BF1[7:4]

0 to +4094

MOD

BF1[3:0], BF2[7:0]

0 to +4095

Nb

BF3[5:0]

0 to +51

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/24FG11PA | CONN RCPT 11POS JAM NUT W/PINS |

| VE-J5J-MW-B1 | CONVERTER MOD DC/DC 36V 100W |

| VE-J4D-MX-F4 | CONVERTER MOD DC/DC 85V 75W |

| LT8500IUHH#PBF | IC PWM GENERATOR 56-QFN |

| VE-J4F-MX-F3 | CONVERTER MOD DC/DC 72V 75W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9577-EVALZ | 制造商:AD 制造商全称:Analog Devices 功能描述:Clock Generator with Dual PLLs |

| AD9578BCPZ | 功能描述:IC PLL CLOCK GEN 20MHZ 48LFCSP 制造商:analog devices inc. 系列:- 包装:托盘 零件状态:有效 类型:* PLL:带旁路 输入:LVCMOS,LVDS,LVPECL,晶体 输出:HCSL,LVCMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:2:5 差分 - 输入:输出:是/是 频率 - 最大值:919MHz 分频器/倍频器:是/无 电压 - 电源:2.375 V ~ 3.63 V 工作温度:-25°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP-VQ(7x7) 标准包装:1 |

| AD9578BCPZ-REEL7 | 功能描述:IC PLL CLOCK GEN 20MHZ 48LFCSP 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:有效 类型:* PLL:带旁路 输入:LVCMOS,LVDS,LVPECL,晶体 输出:HCSL,LVCMOS,LVDS,LVPECL 电路数:1 比率 - 输入:输出:2:5 差分 - 输入:输出:是/是 频率 - 最大值:919MHz 分频器/倍频器:是/无 电压 - 电源:2.375 V ~ 3.63 V 工作温度:-25°C ~ 85°C 安装类型:表面贴装 封装/外壳:48-WFQFN 裸露焊盘,CSP 供应商器件封装:48-LFCSP-VQ(7x7) 标准包装:1 |

| AD95S08KAC | 制造商:未知厂家 制造商全称:未知厂家 功能描述:THYRISTOR MODULE|DOUBLER|HALF-CNTLD|POSITIVE|15V V(RRM)|95A I(T) |

| AD95S08KAF | 制造商:未知厂家 制造商全称:未知厂家 功能描述:THYRISTOR MODULE|DOUBLER|HALF-CNTLD|POSITIVE|15V V(RRM)|95A I(T) |

发布紧急采购,3分钟左右您将得到回复。