- 您现在的位置:买卖IC网 > PDF目录10069 > AD9627ABCPZ-80 (Analog Devices Inc)IC ADC 12BIT 80MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9627ABCPZ-80 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 28/76页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 80MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 80M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 490mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9627

Rev. B | Page 34 of 76

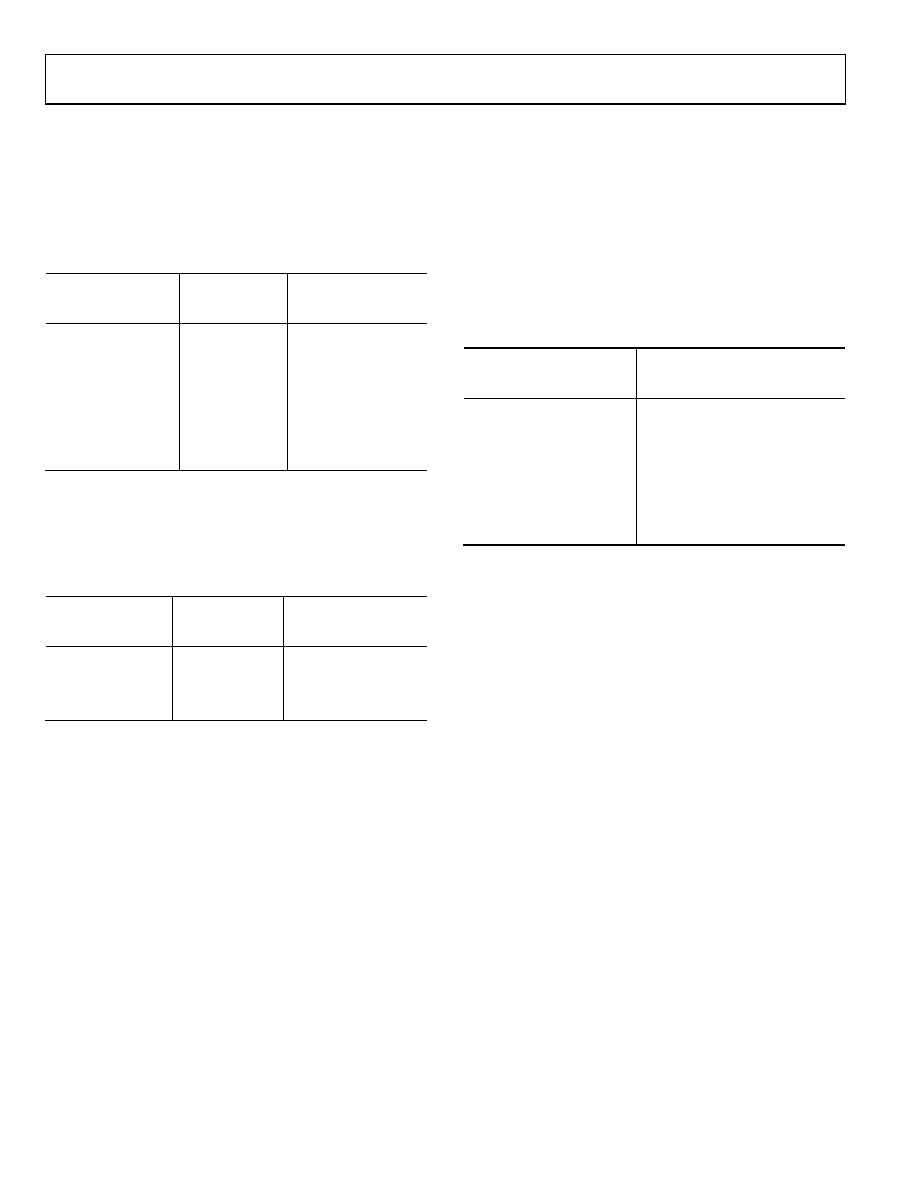

When the fast detect mode select bits are set to 0b001, 0b010, or

0b011, a subset of the fast detect output pins is available. In these

modes, the fast detect output pins have a latency of six clock cycles.

Table 19 shows the corresponding ADC input levels when the

fast detect mode select bits are set to 0b001 (that is, when ADC fast

magnitude is presented on the FD[3:1] pins).

Table 19. ADC Fast Magnitude Nominal Levels with

Fast Detect Mode Select Bits = 001

ADC Fast Magnitude

on FD[3:1] Pins

Nominal Input

Magnitude

Below FS (dB)

Nominal Input

Magnitude

Uncertainty (dB)

000

<24

Minimum to 18.07

001

24 to 14.5

30.14 to 12.04

010

14.5 to 10

18.07 to 8.52

011

10 to 7

12.04 to 6.02

100

7 to 5

8.52 to 4.08

101

5 to 3.25

6.02 to 2.5

110

3.25 to 1.8

4.08 to 1.16

111

1.8 to 0

2.5 to 0

When the fast detect mode select bits are set to 0b010 or 0b011

(that is, when ADC fast magnitude is presented on the FD[3:2]

pins), the LSB is not provided. The input ranges for this mode

are shown in Table 20.

Table 20. ADC Fast Magnitude Nominal Levels with

Fast Detect Mode Select Bits = 010 or 011

ADC Fast

Magnitude on

FD[2:1] Pins

Nominal Input

Magnitude

Below FS (dB)

Nominal Input

Magnitude

Uncertainty (dB)

00

<14.5

Minimum to 12.04

01

14.5 to 7

18.07 to 6.02

10

7 to 3.25

8.52 to 2.5

11

3.25 to 0

4.08 to 0

ADC OVERRANGE (OR)

The ADC overrange indicator is asserted when an overrange is

detected on the input of the ADC. The overrange condition is

determined at the output of the ADC pipeline and, therefore, is

subject to a latency of 12 ADC clock cycles. An overrange at the

input is indicated by this bit 12 clock cycles after it occurs.

GAIN SWITCHING

The AD9627 includes circuitry that is useful in applications either

where large dynamic ranges exist or where gain ranging converters

are employed. This circuitry allows digital thresholds to be set

such that an upper threshold and a lower threshold can be

programmed. Fast detect mode select bit = 010 through fast

detect mode select bit = 101 support various combinations of the

gain switching options.

One such use is to detect when an ADC is about to reach full

scale with a particular input condition. The result is to provide

an indicator that can be used to quickly insert an attenuator that

prevents ADC overdrive.

Coarse Upper Threshold (C_UT)

The coarse upper threshold indicator is asserted if the ADC fast

magnitude input level is greater than the level programmed in

the coarse upper threshold register (Address 0x105[2:0]). This

value is compared with the ADC Fast Magnitude Bits[2:0]. The

coarse upper threshold output is output two clock cycles after the

level is exceeded at the input and, therefore, it provides a fast

indication of the input signal level. The coarse upper threshold

levels are shown in Table 21. This indicator remains asserted for

a minimum of two ADC clock cycles or until the signal drops

below the threshold level.

Table 21. Coarse Upper Threshold Levels

Coarse Upper Threshold

Register 0x105[2:0]

C_UT Is Active When Signal

Magnitude Below FS

Is Greater Than (dB)

000

<24

001

24

010

14.5

011

10

100

7

101

5

110

3.25

111

1.8

Fine Upper Threshold (F_UT)

The fine upper threshold indicator is asserted if the input

magnitude exceeds the value programmed in the fine upper

threshold register located in Register 0x106 and Register 0x107.

The 13-bit threshold register is compared with the signal magni-

tude at the output of the ADC. This comparison is subject to the

ADC clock latency but is accurate in terms of the converter

resolution. The fine upper threshold magnitude is defined by

the following equation:

dBFS = 20 log(Threshold Magnitude/213)

Fine Lower Threshold (F_LT)

The fine lower threshold indicator is asserted if the input

magnitude is less than the value programmed in the fine lower

threshold register located at Register 0x108 and Register 0x109.

The fine lower threshold register is a 13-bit register that is

compared with the signal magnitude at the output of the ADC.

This comparison is subject to ADC clock latency but is accurate

in terms of the converter resolution. The fine lower threshold

magnitude is defined by the following equation:

dBFS = 20 log(Threshold Magnitude/213)

The operation of the fine upper threshold indicators and fine

lower threshold indicators is shown in Figure 67.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BNL-IV-F3 | CONVERTER MOD DC/DC 28V 150W |

| IDT7205L12PDG | IC FIFO 8192X9 12NS 28PDIP |

| VE-BNJ-IV-F3 | CONVERTER MOD DC/DC 36V 150W |

| VE-BNJ-IV-F2 | CONVERTER MOD DC/DC 36V 150W |

| VE-BNF-IV-F3 | CONVERTER MOD DC/DC 72V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9627BCPZ-105 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9627BCPZ11-105 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ11-150 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ-125 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ-150 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 150Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP 制造商:Analog Devices 功能描述:ADC Dual Pipelined 150Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP Tray |

发布紧急采购,3分钟左右您将得到回复。