- 您现在的位置:买卖IC网 > PDF目录10069 > AD9627ABCPZ-80 (Analog Devices Inc)IC ADC 12BIT 80MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9627ABCPZ-80 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 56/76页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 80MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 80M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 490mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9627

Rev. B | Page 6 of 76

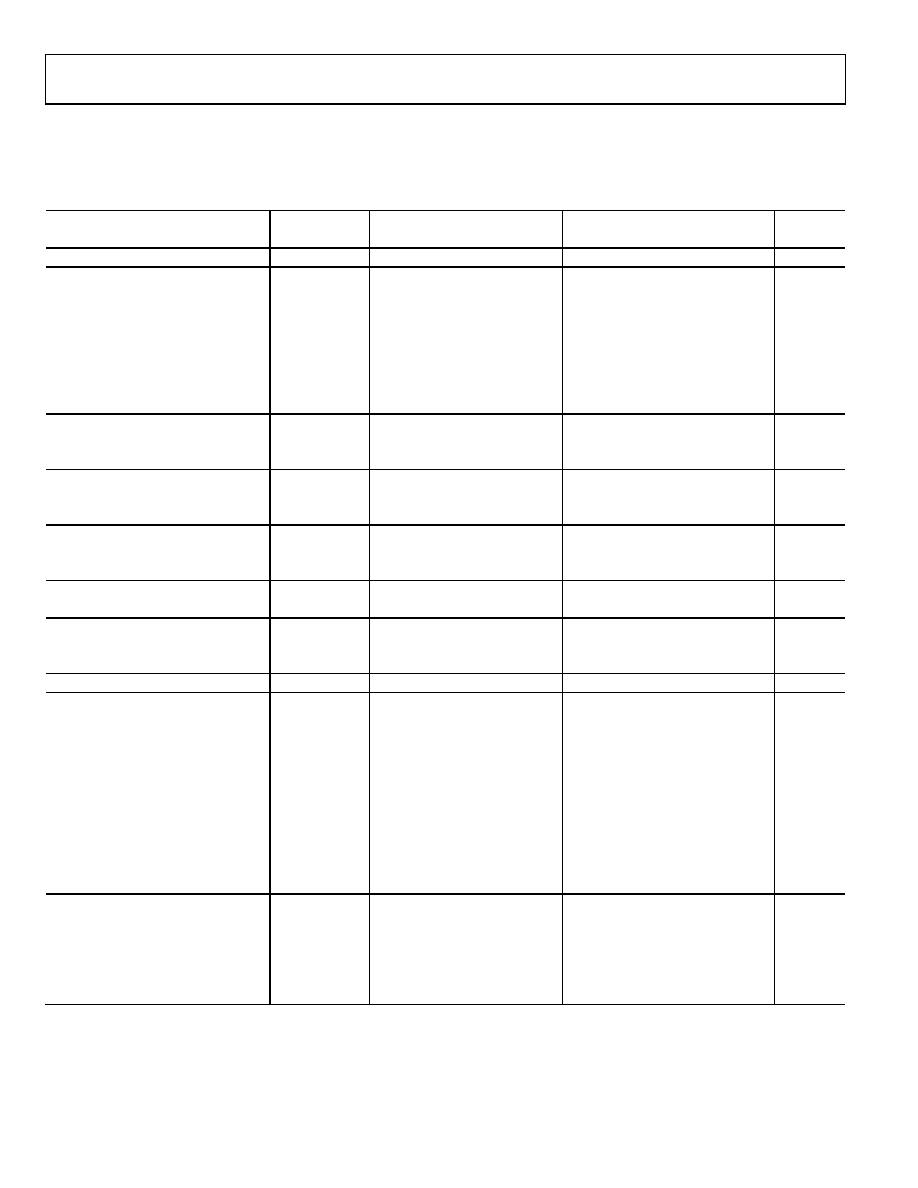

ADC DC SPECIFICATIONS—AD9627-125/AD9627-150

AVDD = 1.8 V, DVDD = 1.8 V, DRVDD = 3.3 V, maximum sample rate, VIN = 1.0 dBFS differential input, 1.0 V internal reference, DCS

enabled, fast detect output pins disabled, and signal monitor disabled, unless otherwise noted.

Table 2.

Parameter

Temperature

AD9627-125

AD9627-150

Unit

Min

Typ

Max

Min

Typ

Max

RESOLUTION

Full

12

Bits

ACCURACY

No Missing Codes

Full

Guaranteed

Offset Error

Full

±0.3

±0.6

±0.2

±0.6

% FSR

Gain Error

Full

0.7

2.7

3.9

0.9

3.2

5.2

% FSR

Differential Nonlinearity (DNL)1

Full

±0.4

±0.9

LSB

25°C

±0.2

LSB

Integral Nonlinearity (INL)1

Full

±0.9

±1.3

LSB

25°C

±0.4

±0.5

LSB

MATCHING CHARACTERISTIC

Offset Error

25°C

±0.3

±0.6

±0.2

±0.7

% FSR

Gain Error

25°C

±0.1

±0.75

±0.2

±0.8

% FSR

TEMPERATURE DRIFT

Offset Error

Full

±15

ppm/°C

Gain Error

Full

±95

ppm/°C

INTERNAL VOLTAGE REFERENCE

Output Voltage Error (1 V Mode)

Full

±5

±16

±5

±16

mV

Load Regulation @ 1.0 mA

Full

7

mV

INPUT REFERRED NOISE

VREF = 1.0 V

25°C

0.3

LSB rms

ANALOG INPUT

Input Span, VREF = 1.0 V

Full

2

V p-p

Input Capacitance2

Full

8

pF

VREF INPUT RESISTANCE

Full

6

kΩ

POWER SUPPLIES

Supply Voltage

AVDD, DVDD

Full

1.7

1.8

1.9

1.7

1.8

1.9

V

DRVDD (CMOS Mode)

Full

1.7

3.3

3.6

1.7

3.3

3.6

V

DRVDD (LVDS Mode)

Full

1.7

1.8

1.9

1.7

1.8

1.9

V

Supply Current

IAVDD1, 3

Full

385

455

419

495

mA

Full

42

50

mA

IDRVDD1 (3.3 V CMOS)

Full

36

42

mA

IDRVDD1 (1.8 V CMOS)

Full

18

22

mA

IDRVDD1 (1.8 V LVDS)

Full

48

49

mA

POWER CONSUMPTION

DC Input

Full

750

800

820

890

mW

Sine Wave Input1 (DRVDD = 1.8 V)

Full

814

895

mW

Sine Wave Input1 (DRVDD = 3.3 V)

Full

900

995

mW

Standby Power4

Full

77

mW

Power-Down Power

Full

2.5

6

2.5

6

mW

1 Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit.

2 Input capacitance refers to the effective capacitance between one differential input pin and AGND. See Figure 8 for the equivalent analog input structure.

3 The maximum limit applies to the combination of IAVDD and IDVDD currents.

4 Standby power is measured with a dc input and with the CLK pins inactive (set to AVDD or AGND).

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BNL-IV-F3 | CONVERTER MOD DC/DC 28V 150W |

| IDT7205L12PDG | IC FIFO 8192X9 12NS 28PDIP |

| VE-BNJ-IV-F3 | CONVERTER MOD DC/DC 36V 150W |

| VE-BNJ-IV-F2 | CONVERTER MOD DC/DC 36V 150W |

| VE-BNF-IV-F3 | CONVERTER MOD DC/DC 72V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9627BCPZ-105 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9627BCPZ11-105 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ11-150 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ-125 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ-150 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 150Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP 制造商:Analog Devices 功能描述:ADC Dual Pipelined 150Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP Tray |

发布紧急采购,3分钟左右您将得到回复。