- 您现在的位置:买卖IC网 > PDF目录10069 > AD9627ABCPZ-80 (Analog Devices Inc)IC ADC 12BIT 80MSPS 64LFCSP PDF资料下载

参数资料

| 型号: | AD9627ABCPZ-80 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 4/76页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 80MSPS 64LFCSP |

| 标准包装: | 1 |

| 位数: | 12 |

| 采样率(每秒): | 80M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 2 |

| 功率耗散(最大): | 490mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 托盘 |

| 输入数目和类型: | 4 个单端,单极;2 个差分,单极 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页

AD9627

Rev. B | Page 12 of 76

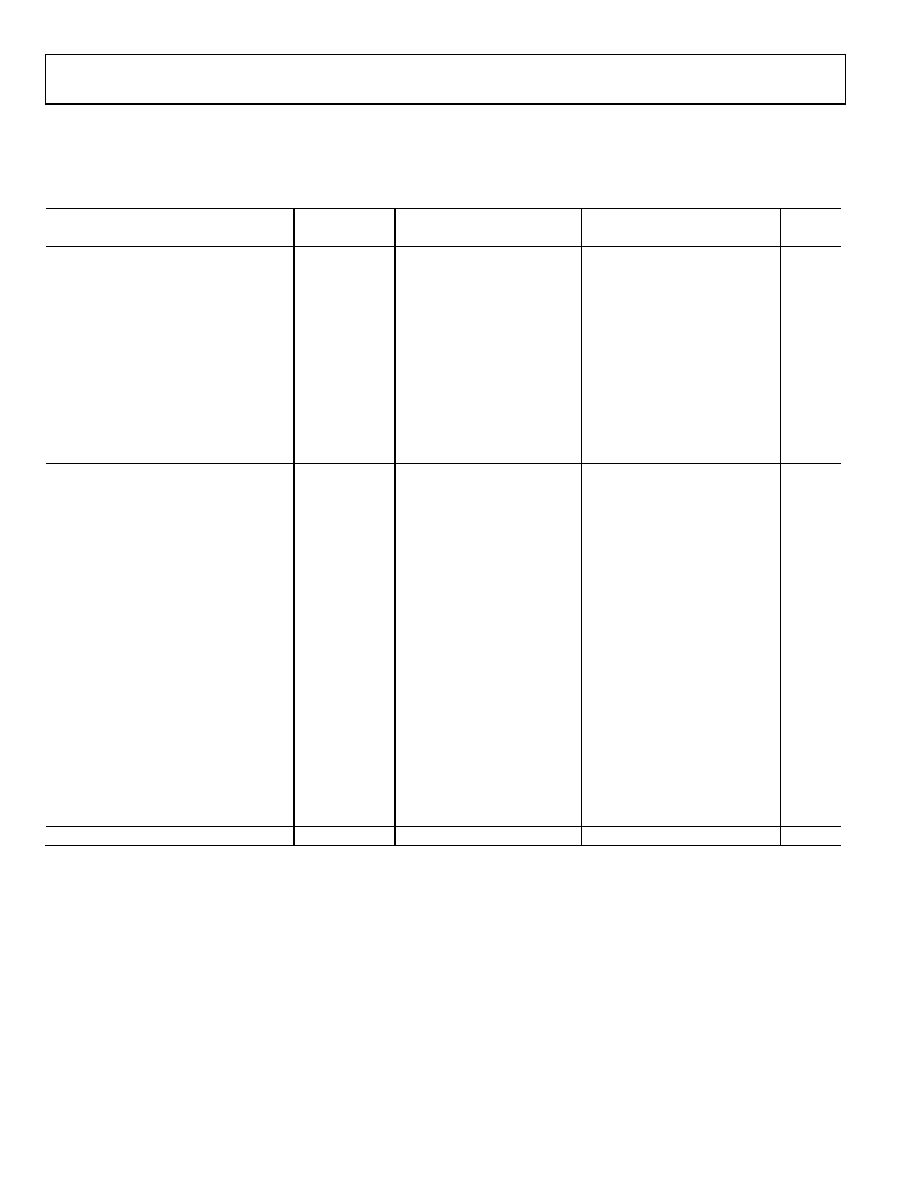

SWITCHING SPECIFICATIONS—AD9627-125/AD9627-150

AVDD = 1.8 V, DVDD = 1.8 V, DRVDD = 3.3 V, maximum sample rate, VIN = 1.0 dBFS differential input, 1.0 V internal reference, and

DCS enabled, unless otherwise noted.

Table 7.

Parameter

Temperature

AD9627-125

AD9627-150

Unit

Min

Typ

Max

Min

Typ

Max

CLOCK INPUT PARAMETERS

Input Clock Rate

Full

625

MHz

Conversion Rate

DCS Enabled1

Full

20

125

20

150

MSPS

DCS Disabled1

Full

10

125

10

150

MSPS

CLK Period—Divide-by-1 Mode (tCLK)

Full

8

6.66

ns

CLK Pulse Width High

Divide-by-1 Mode, DCS Enabled

Full

2.4

4

5.6

2.0

3.33

4.66

ns

Divide-by-1 Mode, DCS Disabled

Full

3.6

4

4.4

3.0

3.33

3.66

ns

Divide-by-2 Mode, DCS Enabled

Full

1.6

ns

Divide-by-3-Through-8 Mode,

DCS Enabled

Full

0.8

ns

DATA OUTPUT PARAMETERS (DATA, FD)

CMOS Mode—DRVDD = 3.3 V

Data Propagation Delay (tPD)2

Full

2.2

4.5

6.4

2.2

4.5

6.4

ns

DCO Propagation Delay (tDCO)

Full

3.8

5.0

6.8

3.8

5.0

6.8

ns

Setup Time (tS)

Full

4.5

3.83

ns

Hold Time (tH)

Full

3.5

2.83

ns

CMOS Mode—DRVDD = 1.8 V

Data Propagation Delay (tPD)2

Full

2.4

5.2

6.9

2.4

5.2

6.9

ns

DCO Propagation Delay (tDCO)

Full

4.0

5.6

7.3

4.0

5.6

7.3

ns

Setup Time (tS)

Full

4.4

3.73

ns

Hold Time (tH)

Full

3.6

2.93

ns

LVDS Mode—DRVDD = 1.8 V

Data Propagation Delay (tPD)2

Full

2.0

4.8

6.3

2.0

4.8

6.3

ns

DCO Propagation Delay (tDCO)

Full

5.2

7.3

9.0

5.2

7.3

9.0

ns

CMOS Mode Pipeline Delay (Latency)

Full

12

Cycles

LVDS Mode Pipeline Delay (Latency)

Channel A/Channel B

Full

12/12.5

Cycles

Aperture Delay (tA)

Full

1.0

ns

Aperture Uncertainty (Jitter, tJ)

Full

0.1

ps rms

Wake-Up Time3

Full

350

μs

OUT-OF-RANGE RECOVERY TIME

Full

3

Cycles

1 Conversion rate is the clock rate after the divider.

2 Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with 5 pF load.

3 Wake-up time is dependent on the value of the decoupling capacitors.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-BNL-IV-F3 | CONVERTER MOD DC/DC 28V 150W |

| IDT7205L12PDG | IC FIFO 8192X9 12NS 28PDIP |

| VE-BNJ-IV-F3 | CONVERTER MOD DC/DC 36V 150W |

| VE-BNJ-IV-F2 | CONVERTER MOD DC/DC 36V 150W |

| VE-BNF-IV-F3 | CONVERTER MOD DC/DC 72V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9627BCPZ-105 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 105Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP |

| AD9627BCPZ11-105 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ11-150 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ-125 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD9627BCPZ-150 | 制造商:Analog Devices 功能描述:ADC Dual Pipelined 150Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP 制造商:Analog Devices 功能描述:ADC Dual Pipelined 150Msps 12-bit Parallel/LVDS 64-Pin LFCSP EP Tray |

发布紧急采购,3分钟左右您将得到回复。