参数资料

| 型号: | ADATE207BBPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 34/36页 |

| 文件大小: | 0K |

| 描述: | IC TIMING FORMATTER QUAD 256BGA |

| 标准包装: | 1 |

| 类型: | 四针定时格式器 |

| PLL: | 是 |

| 主要目的: | 自动测试设备 |

| 电路数: | 4 |

| 频率 - 最大: | 100MHz |

| 电源电压: | 2.375 V ~ 2.625 V |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA 裸露焊盘 |

| 供应商设备封装: | 256-BGA(27x27) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页当前第34页第35页第36页

ADATE207

Rev. 0 | Page 7 of 36

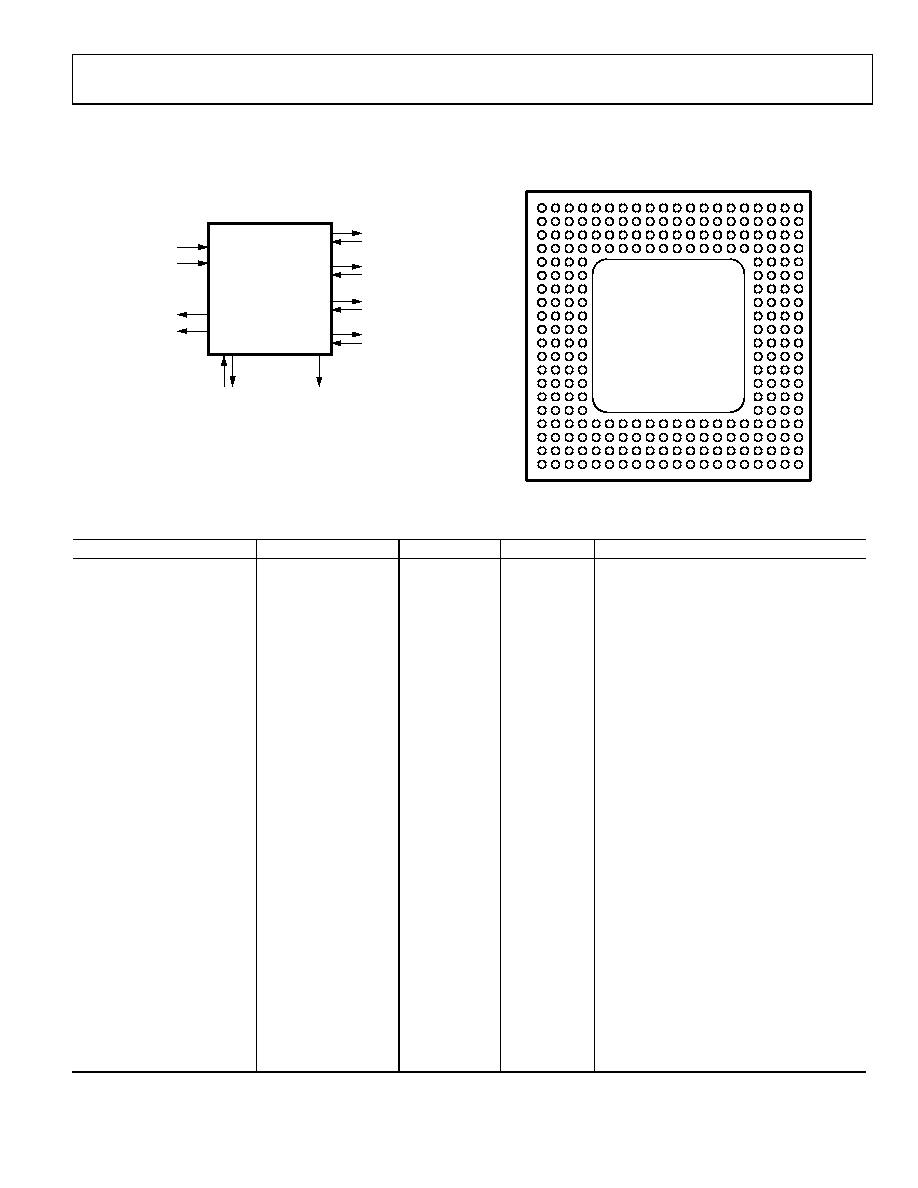

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

ADATE207

PATTERN DATA

PERIOD DATA

COMPARE FAILS

RECEIVE DATA

CH3 DCL I/F

CH2 DCL I/F

CH1 DCL I/F

CH0 DCL I/F

COMMAND/

STATUS BUS

TIME

MEASUREMENT

05

55

7-

0

09

Figure 5. Connection Overview Diagram

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

2

4

6

8

10

12

14

16

18

20

1

3

5

7

9

11

13

15

17

19

BOTTOM

VIEW

(Not to Scale)

ADATE207

05

55

7-

0

14

Figure 6. Ball Grid Array

Table 7. Pin Function Descriptions

Pin No.

Mnemonic

Input/Output1

Type

Description

B4, A4, C5, D6

PAT_MASK[3:0]

I

LVCMOS25

Mask Failures. Used to mask failures on D3,

D2, D1 and D0 edges, respectively. Clocked

by MCLK.

T3, U1, U2, T4, U3, V4, U5, W4

PAT_PATDATA_0[7:0]

I

LVCMOS25

Channel 0 Waveform Memory Address. Use

these pins to address waveform memory for

Channel 0. Clocked by MCLK.

B5, A5, C6, B6, A6, C7, B7, D8

PAT_PATDATA_1[7:0]

I

LVCMOS25

Channel 1 Waveform Memory Address. Use

these pins to address waveform memory for

Channel 1. Clocked by MCLK.

W212, V12, Y13, U12, W13,

V13, Y14, W14

PAT_PATDATA_2[7:0]

I

LVCMOS25

Channel 2 Waveform Memory Address. Use

these pins to address waveform memory for

Channel 2. Clocked by MCLK.

A16, B16, D15, C16, A17,

B17, D16, C17

PAT_PATDATA_3[7:0]

I

LVCMOS25

Channel 3 Waveform Memory Address. Use

these pins to address waveform memory for

Channel 3. Clocked by MCLK.

Y4, W5, V6

PAT_FAIL_0[3:0]

O

LVCMOS25

Fails on D3, D2, D1 and D0 Edges for Channel 0.

Clocked by MCLK.

B8, A8, B9, B10

PAT_FAIL_1[3:0]

O

LVCMOS25

Fails on D3, D2, D1 and D0 Edges for Channel 1.

Clocked by MCLK.

V8, W8, W9, Y9

PAT_FAIL_2[3:0]

O

LVCMOS25

Fails on D3, D2, D1 and D0 Edges for Channel 2.

Clocked by MCLK.

B12, C12, B13, A14

PAT_FAIL_3[3:0]

O

LVCMOS25

Fails on D3, D2, D1 and D0 Edges for Channel 3.

Clocked by MCLK.

W6, Y6, W7, Y7

PAT_DUTDATA_0[3:0]

O

LVCMOS25

DUT Capture Data from Channel 0. Clocked

by MCLK.

C10, A11, B11, A12

PAT_DUTDATA_1[3:0]

O

LVCMOS25

DUT Capture Data from Channel 1. Clocked

by MCLK.

V10, W10, Y10, W11

PAT_DUTDATA_2[3:0]

O

LVCMOS25

DUT Capture Data from Channel 2. Clocked

by MCLK.

B14, C14, A15, B15

PAT_DUTDATA_3[3:0]

O

LVCMOS25

DUT Capture Data from Channel 3. Clocked

by MCLK.

相关PDF资料 |

PDF描述 |

|---|---|

| ADC0804LCN | IC ADC 8-BIT 10KSPS 1LSB 20-DIP |

| ADC0820CCM+ | IC ADC 8-BIT HS 20-SOIC |

| ADF4001BRU | IC CLOCK GEN PLL 16-TSSOP |

| ADF4002BRUZ-RL7 | IC PLL FREQUENCY SYNTH 16-TSSOP |

| ADF4007BCPZ-RL7 | IC DIVIDER/PLL SYNTHESZR 20LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADATE209 | 制造商:AD 制造商全称:Analog Devices 功能描述:4.0 Gbps Dual Driver |

| ADATE209BBCZ | 制造商:Analog Devices 功能描述:4.0 GBPS DUAL DRIVER - Rail/Tube |

| ADATE209BCPZ | 制造商:Analog Devices 功能描述: |

| ADATE302-02 | 制造商:AD 制造商全称:Analog Devices 功能描述:500 MHz Dual Integrated DCL with Differential Drive/Receive, Level Setting DACs, and Per Pin PMU |

| ADATE302-02BBCZ | 功能描述:IC DCL ATE 500MHZ DUAL 84CSPBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。