参数资料

| 型号: | ADATE207BBPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 8/36页 |

| 文件大小: | 0K |

| 描述: | IC TIMING FORMATTER QUAD 256BGA |

| 标准包装: | 1 |

| 类型: | 四针定时格式器 |

| PLL: | 是 |

| 主要目的: | 自动测试设备 |

| 电路数: | 4 |

| 频率 - 最大: | 100MHz |

| 电源电压: | 2.375 V ~ 2.625 V |

| 工作温度: | -25°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LBGA 裸露焊盘 |

| 供应商设备封装: | 256-BGA(27x27) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

ADATE207

Rev. 0 | Page 16 of 36

After the power and MCLK inputs are stable, the device must be

reset using the hard reset and error reset bits. The soft reset can

be used to initialize registers at any time and does not reset the

PLL or FIFOs.

There are six rules of reset.

Rule 1—on power up, keep the hard reset pin (RESET_B)

asserted.

Rule 2—if MCLK is unstable, keep the hard reset pin

(RESET_B) asserted.

Rule 3—after MCLK is stable, keep the hard reset pin

(RESET_B) asserted for at least 20 μs.

Rule 4—after the 20 μs of Rule 3 has elapsed, assert the error

reset bit (Bit 03 in Register 0x19).

Rule 5—the hard reset signal (RESET_B) can be asserted

asynchronously to MCLK, but upon deassertion, must make

setup and hold requirements upon the MCLK.

Rule 6—the minimum pulse width of RESET_B must be at least

three MCLK periods.

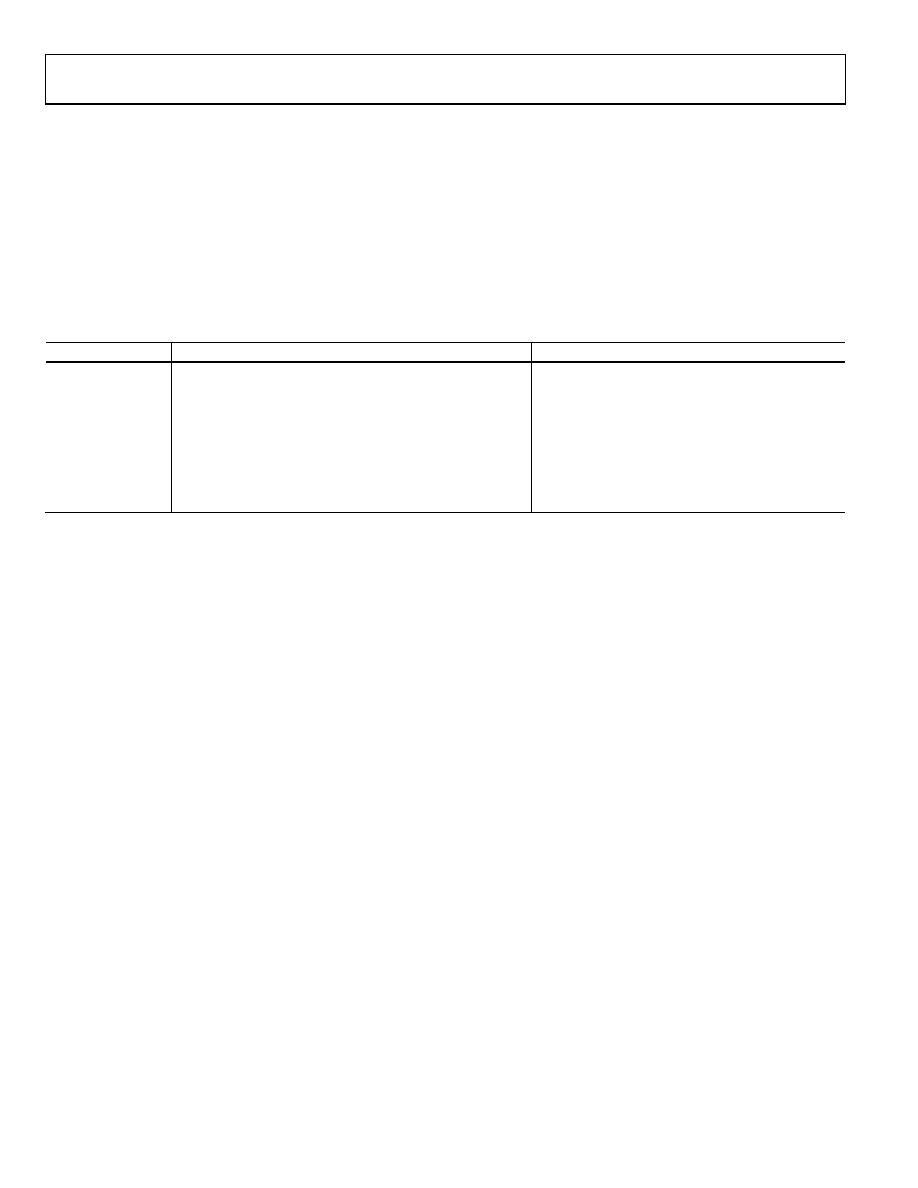

Table 11. Comparison Between Normal Mode and Clock Generation Mode

Normal Mode (CLKGEN_MD_EN=0)

Clock Generator Mode(CLKGEN_MD_EN=1)

Period Start

A single signal for all four channels, I_PER_EARLY_T0EN.

Four signals, one per channel; PAT_MASK[N] operates

as a period start signal for channel N.

Waveform

Memory Selection

Each channel N is selected via the I_PAT_PATDATA_N vector

every rising edge of I_MCLK.

Waveform memory location is fixed at Address 0.

Input Delay

A single vector adjust input delay for all channels,

INPUT_DELAY.

Four vectors are available, one per channel. For each

Channel N, PAT_PATDATA_N operates as

INPUT_DELAY for Channel N.

Fail Masking

Edge N for all channels can mask the fail operation every

rising edge of I_MCLK via PAT_MASK[N].

No masking of fail operations is available.

相关PDF资料 |

PDF描述 |

|---|---|

| ADC0804LCN | IC ADC 8-BIT 10KSPS 1LSB 20-DIP |

| ADC0820CCM+ | IC ADC 8-BIT HS 20-SOIC |

| ADF4001BRU | IC CLOCK GEN PLL 16-TSSOP |

| ADF4002BRUZ-RL7 | IC PLL FREQUENCY SYNTH 16-TSSOP |

| ADF4007BCPZ-RL7 | IC DIVIDER/PLL SYNTHESZR 20LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADATE209 | 制造商:AD 制造商全称:Analog Devices 功能描述:4.0 Gbps Dual Driver |

| ADATE209BBCZ | 制造商:Analog Devices 功能描述:4.0 GBPS DUAL DRIVER - Rail/Tube |

| ADATE209BCPZ | 制造商:Analog Devices 功能描述: |

| ADATE302-02 | 制造商:AD 制造商全称:Analog Devices 功能描述:500 MHz Dual Integrated DCL with Differential Drive/Receive, Level Setting DACs, and Per Pin PMU |

| ADATE302-02BBCZ | 功能描述:IC DCL ATE 500MHZ DUAL 84CSPBGA RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。