- 您现在的位置:买卖IC网 > PDF目录2063 > ADAU1461WBCPZ-R7 (Analog Devices Inc)IC SIGMADSP 24BIT 96KHZ PLL 32 PDF资料下载

参数资料

| 型号: | ADAU1461WBCPZ-R7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 39/88页 |

| 文件大小: | 0K |

| 描述: | IC SIGMADSP 24BIT 96KHZ PLL 32 |

| 标准包装: | 1,500 |

| 系列: | SigmaDSP® |

| 类型: | 音频处理器 |

| 应用: | 车载音频 |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-VQ |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页当前第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

ADAU1461

Rev. 0 | Page 44 of 88

NUMERIC FORMATS

DSP systems commonly use a standard numeric format.

Fractional numeric systems are specified by an A.B format,

where A is the number of bits to the left of the decimal point

and B is the number of bits to the right of the decimal point.

The ADAU1461 uses numeric format 5.23 for both the

parameter and data values.

Numeric Format 5.23

Linear range: 16.0 to (+16.0 1 LSB)

Examples:

1000 0000 0000 0000 0000 0000 0000 = 16.0

1110 0000 0000 0000 0000 0000 0000 = 4.0

1111 1000 0000 0000 0000 0000 0000 = 1.0

1111 1110 0000 0000 0000 0000 0000 = 0.25

1111 1111 0011 0011 0011 0011 0011 = 0.1

1111 1111 1111 1111 1111 1111 1111 = (1 LSB below 0)

0000 0000 0000 0000 0000 0000 0000 = 0

0000 0000 1100 1100 1100 1100 1101 = 0.1

0000 0010 0000 0000 0000 0000 0000 = 0.25

0000 1000 0000 0000 0000 0000 0000 = 1.0

0010 0000 0000 0000 0000 0000 0000 = 4.0

0111 1111 1111 1111 1111 1111 1111 = (16.0 1 LSB)

The serial port accepts up to 24 bits on the input and is sign-

extended to the full 28 bits of the DSP core. This allows internal

gains of up to 24 dB without internal clipping.

A digital clipper circuit is used between the output of the DSP

core and the DACs or serial port outputs (see Figure 68). This

circuit clips the top four bits of the signal to produce a 24-bit

output with a range of 1.0 (minus 1 LSB) to 1.0. Figure 68

shows the maximum signal levels at each point in the data flow

in both binary and decibel levels.

4-BIT SIGN EXTENSION

DATA IN

1.23

(0dB)

1.23

(0dB)

1.23

(0dB)

5.23

(24dB)

5.23

(24dB)

SERIAL

PORT

SIGNAL

PROCESSING

(5.23 FORMAT)

DIGITAL

CLIPPER

089

14

-0

68

Figure 68. Numeric Precision and Clipping Structure

PROGRAMMING

On power-up, the ADAU1461 must be configured with a clock-

ing scheme and then loaded with register settings. After the codec

signal path is set up, the DSP core can be programmed. There

are 1024 instruction cycles per audio sample, resulting in an

internal clock rate of 49.152 MHz when fS = 48 kHz.

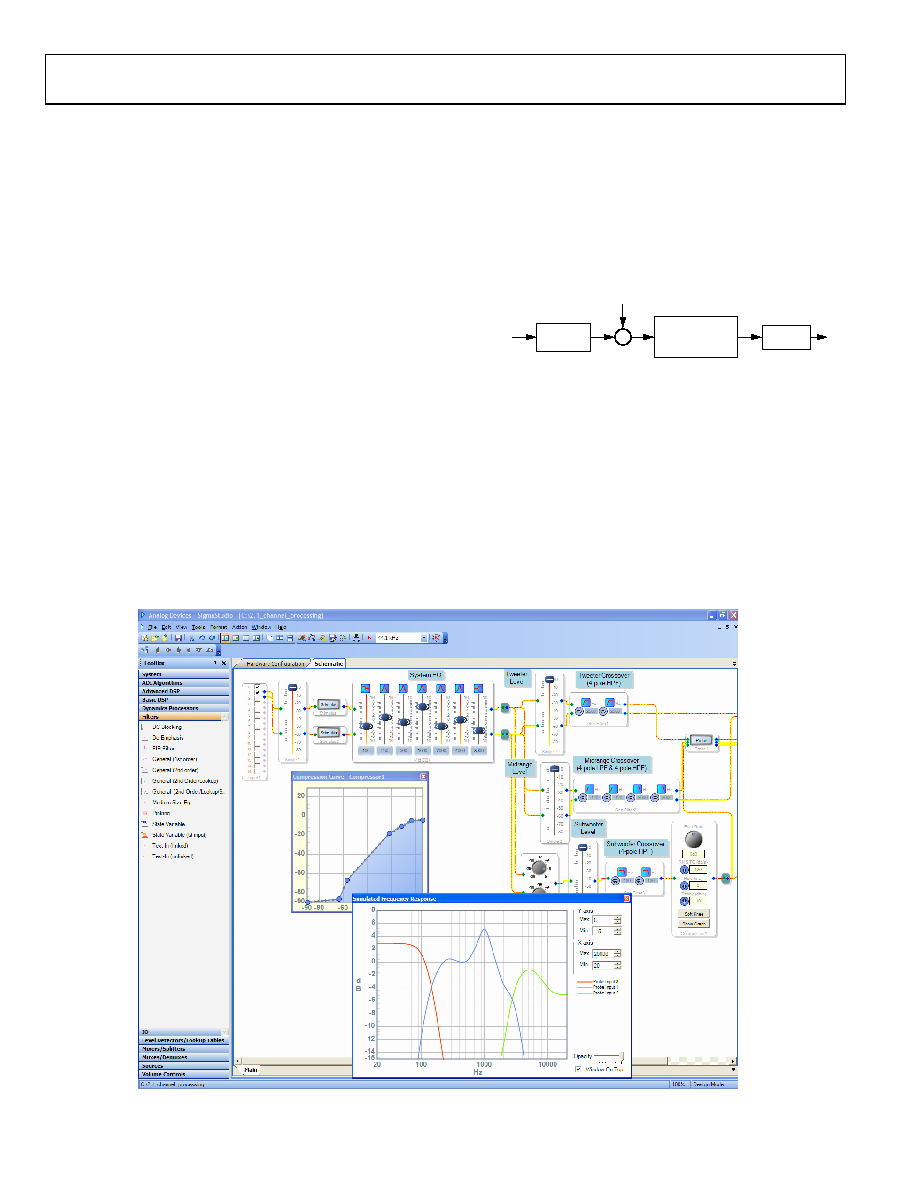

The part can be programmed easily using SigmaStudio, a graphical

tool provided by Analog Devices (see Figure 69). No knowledge

of writing line-level DSP code is required. More information

about SigmaStudio can be found at www.analog.com.

0

8914-

069

Figure 69. SigmaStudio Screen Shot

相关PDF资料 |

PDF描述 |

|---|---|

| ADAU1513ACPZ-RL7 | IC AMP AUDIO PWR 23W 48LFCSP |

| ADAU1590ACPZ-RL7 | IC AMP AUDIO PWR 48LFCSP |

| ADAU1592ACPZ | IC AMP AUDIO PWR 24W 48LFCSP |

| ADAU1701JSTZ-RL | IC AUDIO PROC 2ADC/4DAC 48-LQFP |

| ADAU1702JSTZ-RL | IC AUDIO PROC 2ADC/4DAC 48-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADAU1461WBCPZ-RL | 功能描述:IC SIGMADSP 24BIT 96KHZ PLL 32 RoHS:是 类别:集成电路 (IC) >> 线性 - 音频处理 系列:SigmaDSP® 其它有关文件:STA321 View All Specifications 标准包装:1 系列:Sound Terminal™ 类型:音频处理器 应用:数字音频 安装类型:表面贴装 封装/外壳:64-LQFP 裸露焊盘 供应商设备封装:64-LQFP EP(10x10) 包装:Digi-Reel® 其它名称:497-11050-6 |

| ADAU1462WBCPZ150 | 功能描述:32BIT SIGMADSP AUDIO 16K/48K 制造商:analog devices inc. 系列:* 包装:管件 零件状态:在售 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP(10x10) 标准包装:1 |

| ADAU1462WBCPZ150RL | 功能描述:32BIT SIGMADSP AUDIO 16K/48K 制造商:analog devices inc. 系列:* 包装:带卷(TR) 零件状态:在售 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP(10x10) 标准包装:2,000 |

| ADAU1462WBCPZ300 | 功能描述:32BIT SIGMADSP AUDIO 16K/48K 制造商:analog devices inc. 系列:* 包装:管件 零件状态:在售 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP(10x10) 标准包装:1 |

| ADAU1462WBCPZ300RL | 功能描述:32BIT SIGMADSP AUDIO 16K/48K 制造商:analog devices inc. 系列:* 包装:带卷(TR) 零件状态:在售 安装类型:表面贴装 封装/外壳:72-VFQFN 裸露焊盘,CSP 供应商器件封装:72-LFCSP(10x10) 标准包装:2,000 |

发布紧急采购,3分钟左右您将得到回复。