- 您现在的位置:买卖IC网 > PDF目录16806 > ADM1166ACPZ (Analog Devices Inc)IC SEQUENCER/SUPERVISOR 40LFCSP PDF资料下载

参数资料

| 型号: | ADM1166ACPZ |

| 厂商: | Analog Devices Inc |

| 文件页数: | 27/32页 |

| 文件大小: | 0K |

| 描述: | IC SEQUENCER/SUPERVISOR 40LFCSP |

| 标准包装: | 1 |

| 系列: | Super Sequencer® |

| 应用: | 电源监控器,序列发生器 |

| 输入电压: | 3 V ~ 14.4 V |

| 电源电压: | 3 V ~ 14.4 V |

| 电流 - 电源: | 4.2mA |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 40-LFCSP-WQ(6x6) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页

�� �

�

�

�ADM1166�

�The� device� also� has� several� identification� registers� (read-only)�

�that� can� be� read� across� the� SMBus.� Table� 12� lists� these� registers�

�with� their� values� and� functions.�

�All� other� devices� on� the� bus� remain� idle� while� the� selected�

�device� waits� for� data� to� be� read� from� or� written� to� it.� If� the�

�R/W� bit� is� a� 0,� the� master� writes� to� the� slave� device.� If� the�

�Table� 12.� Identification� Register� Values� and� Functions�

�Name� Address� Value� Function�

�MANID� 0xF4� 0x41� Manufacturer� ID� for� Analog�

�Devices�

�REVID� 0xF5� 0x02� Silicon� revision�

�MARK1� 0xF6� 0x00� Software� brand�

�MARK2� 0xF7� 0x00� Software� brand�

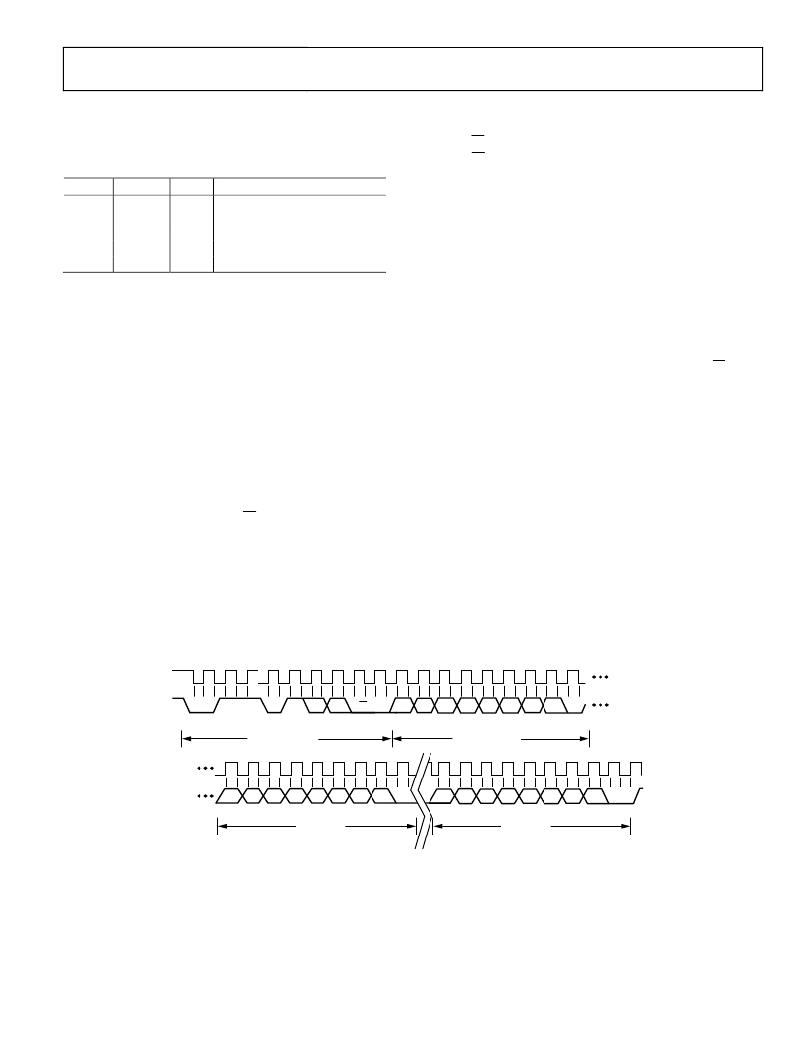

�General� SMBus� Timing�

��read� and� write� operations� using� the� SMBus.� The� SMBus� specification�

�defines� specific� conditions� for� different� types� of� read� and� write�

�operations,� which� are� discussed� in� the� Write� Operations� and� the�

�Read� Operations� sections.�

�The� general� SMBus� protocol� operates� in� the� following� three� steps.�

�2.�

�R/W� bit� is� a� 1,� the� master� reads� from� the� slave� device.�

�Data� is� sent� over� the� serial� bus� in� sequences� of� nine� clock�

�pulses:� eight� bits� of� data� followed� by� an� acknowledge� bit�

�from� the� slave� device.� Data� transitions� on� the� data� line�

�must� occur� during� the� low� period� of� the� clock� signal� and�

�remain� stable� during� the� high� period� because� a� low-to-high�

�transition� when� the� clock� is� high� could� be� interpreted� as� a�

�stop� signal.� If� the� operation� is� a� write� operation,� the� first�

�data� byte� after� the� slave� address� is� a� command� byte.� This�

�command� byte� tells� the� slave� device� what� to� expect� next.� It�

�may� be� an� instruction� telling� the� slave� device� to� expect� a�

�block� write,� or� it� may� be� a� register� address� that� tells� the�

�slave� where� subsequent� data� is� to� be� written.� Because� data�

�can� flow� in� only� one� direction,� as� defined� by� the� R/W� bit,�

�sending� a� command� to� a� slave� device� during� a� read� operation�

�is� not� possible.� Before� a� read� operation,� it� may� be� necessary�

�1.�

�The� master� initiates� data� transfer� by� establishing� a� start�

�condition,� defined� as� a� high-to-low� transition� on� the� serial�

�data� line� SDA,� while� the� serial� clock� line� SCL� remains� high.�

�This� indicates� that� a� data� stream� follows.� All� slave� peripherals�

�connected� to� the� serial� bus� respond� to� the� start� condition�

�and� shift� in� the� next� eight� bits,� consisting� of� a� 7-bit� slave�

�address� (MSB� first)� plus� an� R/W� bit.� This� bit� determines�

�the� direction� of� the� data� transfer,� that� is,� whether� data� is�

�written� to� or� read� from� the� slave� device� (0� =� write,� 1� =� read).�

�The� peripheral� whose� address� corresponds� to� the� transmitted�

�address� responds� by� pulling� the� data� line� low� during� the�

�low� period� before� the� ninth� clock� pulse,� known� as� the�

�3.�

�to� perform� a� write� operation� to� tell� the� slave� what� sort� of�

�read� operation� to� expect� and/or� the� address� from� which�

�data� is� to� be� read.�

�When� all� data� bytes� have� been� read� or� written,� stop� conditions�

�are� established.� In� write� mode,� the� master� pulls� the� data� line�

�high� during� the� 10� th� clock� pulse� to� assert� a� stop� condition.�

�In� read� mode,� the� master� device� releases� the� SDA� line� during�

�the� low� period� before� the� ninth� clock� pulse,� but� the� slave� device�

�does� not� pull� it� low.� This� is� known� as� a� no� acknowledge.�

�The� master� then� takes� the� data� line� low� during� the� low�

�period� before� the� 10� th� clock� pulse� and� then� high� during� the�

�10� th� clock� pulse� to� assert� a� stop� condition.�

�acknowledge� bit,� and� by� holding� it� low� during� the� high� period�

�of� this� clock� pulse.�

�1�

�9�

�1�

�9�

�SCL�

�SDA�

�0�

�1�

�1�

�0�

�1�

�A1�

�A0�

�R/W�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�START� BY�

�MASTER�

�FRAME� 1�

�SLAVE� ADDRESS�

�ACK.� BY�

�SLAVE�

�FRAME� 2�

�COMMAND� CODE�

�ACK.� BY�

�SLAVE�

�1�

�9�

�1�

�9�

�SCL�

�(CONTINUED)�

�SDA�

�(CONTINUED)�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�D7�

�D6�

�D5�

�D4�

�D3�

�D2�

�D1�

�D0�

�ACK.� BY�

�ACK.� BY�

�STOP�

�FRAME� 3�

�DATA� BYTE�

�SLAVE�

�FRAME� N�

�DATA� BYTE�

�SLAVE�

�BY�

�MASTER�

�Figure� 36.� General� SMBus� Write� Timing� Diagram�

�Rev.� 0� |� Page� 27� of� 32�

�相关PDF资料 |

PDF描述 |

|---|---|

| 0982661057 | CBL 35POS 0.5MM JMPR TYPE A 3" |

| H3AAS-1406G | IDC CABLE - HSC14S/AE14G/HSC14S |

| V300B3V3E100B2 | CONVERTER MOD DC/DC 3.3V 100W |

| H2MXS-1406M | DIP CABLE - HDM14S/AE14M/X |

| GCM12DRYN-S13 | CONN EDGECARD 24POS .156 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADM1166ACPZ-REEL | 功能描述:IC SEQUENCER/SUPERVISOR 40LFCSP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:Super Sequencer® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ADM1166ARTZ | 制造商:Analog Devices 功能描述:SUPER SEQUENCER W/ BLACK BOX - Tape and Reel |

| ADM1166ASUZ | 功能描述:IC SEQUENCER/SUPERVISOR 48TQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:Super Sequencer® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ADM1166ASUZ-REEL | 功能描述:IC SEQUENCER/SUPERVISOR 48TQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:Super Sequencer® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ADM1166ASUZ-REEL7 | 功能描述:IC SEQUENCER/SUPERVISOR 48TQFP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:Super Sequencer® 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。